# TR-338 Reverse Power Feed Testing

Issue: 2

Issue Date: August 2020

#### **Notice**

The Broadband Forum is a non-profit corporation organized to create guidelines for broadband network system development and deployment. This Technical Report has been approved by members of the Forum. This Technical Report is subject to change. This Technical Report is owned and copyrighted by the Broadband Forum, and all rights are reserved. Portions of this Technical Report may be owned and/or copyrighted by Broadband Forum members.

#### **Intellectual Property**

Recipients of this Technical Report are requested to submit, with their comments, notification of any relevant patent claims or other intellectual property rights of which they may be aware that might be infringed by any implementation of this Technical Report, or use of any software code normatively referenced in this Technical Report, and to provide supporting documentation.

#### **Terms of Use**

#### 1. License

Broadband Forum hereby grants you the right, without charge, on a perpetual, non-exclusive and worldwide basis, to utilize the Technical Report for the purpose of developing, making, having made, using, marketing, importing, offering to sell or license, and selling or licensing, and to otherwise distribute, products complying with the Technical Report, in all cases subject to the conditions set forth in this notice and any relevant patent and other intellectual property rights of third parties (which may include members of Broadband Forum). This license grant does not include the right to sublicense, modify or create derivative works based upon the Technical Report except to the extent this Technical Report includes text implementable in computer code, in which case your right under this License to create and modify derivative works is limited to modifying and creating derivative works of such code. For the avoidance of doubt, except as qualified by the preceding sentence, products implementing this Technical Report are not deemed to be derivative works of the Technical Report.

#### 2. NO WARRANTIES

THIS TECHNICAL REPORT IS BEING OFFERED WITHOUT ANY WARRANTY WHATSOEVER, AND IN PARTICULAR, ANY WARRANTY OF NONINFRINGEMENT AND ANY IMPLIED WARRANTIES ARE EXPRESSLY DISCLAIMED. ANY USE OF THIS TECHNICAL REPORT SHALL BE MADE ENTIRELY AT THE USER'S OR IMPLEMENTER'S OWN RISK, AND NEITHER THE BROADBAND FORUM, NOR ANY OF ITS MEMBERS OR SUBMITTERS, SHALL HAVE ANY LIABILITY WHATSOEVER TO ANY USER, IMPLEMENTER, OR THIRD PARTY FOR ANY DAMAGES OF ANY NATURE WHATSOEVER, DIRECTLY OR INDIRECTLY, ARISING FROM THE USE OF THIS TECHNICAL REPORT, INCLUDING BUT NOT LIMITED TO, ANY CONSEQUENTIAL, SPECIAL, PUNITIVE, INCIDENTAL, AND INDIRECT DAMAGES.

#### 3. THIRD PARTY RIGHTS

Without limiting the generality of Section 2 above, BROADBAND FORUM ASSUMES NO RESPONSIBILITY TO COMPILE, CONFIRM, UPDATE OR MAKE PUBLIC ANY THIRD PARTY ASSERTIONS OF PATENT OR OTHER INTELLECTUAL PROPERTY RIGHTS THAT MIGHT NOW OR IN THE FUTURE BE INFRINGED BY AN IMPLEMENTATION OF THE TECHNICAL REPORT IN ITS CURRENT, OR IN ANY FUTURE FORM. IF ANY SUCH RIGHTS ARE DESCRIBED ON THE TECHNICAL REPORT, BROADBAND FORUM TAKES NO POSITION AS TO THE VALIDITY OR INVALIDITY OF SUCH ASSERTIONS, OR THAT ALL SUCH ASSERTIONS THAT HAVE OR MAY BE MADE ARE SO LISTED.

All copies of this Technical Report (or any portion hereof) must include the notices, legends, and other provisions set forth on this page.

# **Issue History**

| Issue Number  | Approval Date       | <b>Publication Date</b> | Issue Editor                 | Changes                            |

|---------------|---------------------|-------------------------|------------------------------|------------------------------------|

| 1             | 9 April 2018        | 5 July 2018             | Aleksandra Kozarev,<br>Intel | Original                           |

| 1 Amendment 1 | 2 September<br>2019 | 2 September<br>2019     | Aleksandra Kozarev,<br>Intel | Added Appendix I                   |

| 2             | 25 August<br>2020   | 25 August 2020          | Aleksandra Kozarev,<br>Intel | As listed in the Executive Summary |

Comments or questions about this Broadband Forum Technical Report should be directed to info@broadband-forum.org .

**Editor** Aleksandra Kozarev Intel

**Physical Layer** Transmission **WA Director**

Herman Verbueken Nokia

G.fast & RPF Frank Van der Putten

**Certification Testing PS** Leader

# **Table of Contents**

| E | xecutiv      | re Summary                                            | . 8 |

|---|--------------|-------------------------------------------------------|-----|

| 1 | Pur          | pose and Scope                                        | . 9 |

|   | 1.1          | Purpose                                               |     |

|   | 1.2          | Scope                                                 |     |

| 2 | Ref          | erences and Terminology                               | 10  |

|   | 2.1          | Conventions                                           |     |

|   | 2.2          | References                                            |     |

|   | 2.3          | Definitions                                           |     |

| _ |              |                                                       |     |

| 3 |              | hnical Report Impact                                  |     |

|   | 3.1          | Energy Efficiency                                     |     |

|   | 3.2          | Security Privacy                                      |     |

|   |              |                                                       |     |

| 4 | Con          | nmon Test Information                                 | 14  |

|   | 4.1          | Compliance Requirements                               |     |

|   | 4.2          | Test Plan Passing Criteria                            | 14  |

| 5 | Equ          | ipment Features                                       | 15  |

|   | 5.1          | System Information.                                   | 15  |

| c |              |                                                       |     |

| 6 | res          | t Environments                                        |     |

|   | 6.1          | Test setup                                            |     |

|   | 6.1.<br>6.1. |                                                       |     |

|   | 6.1.         | 3                                                     |     |

|   | 6.1.         |                                                       |     |

| 7 | PSE          | E standalone functional testing                       | 32  |

|   | 7.1          | ELC testing during start-up                           |     |

|   | 7.1.         |                                                       |     |

|   | 7.1.         |                                                       |     |

|   | 7.1.         |                                                       |     |

|   | 7.1.         |                                                       |     |

|   | 7.2          | Start-up tests  1 Line detection test during start-up |     |

|   | 7.2.<br>7.2. |                                                       | 36  |

|   | 7.2.         | 3 Start-up in presence of MELT signature              |     |

|   | 7.3          | Normal operation tests.                               | 37  |

|   | 7.3.         |                                                       |     |

|   | 7.3.         |                                                       |     |

|   | 7.3.<br>7.3. | ,                                                     |     |

|   | 7.3.         | POTS Remote Copper Reconfiguration (PRP) testing.     |     |

|   | 7.5          | Reverse Power Feed (RPF) Noise tests                  |     |

|   | 7.6          | PSE Touch current test                                |     |

|   | 7.6.         |                                                       |     |

|   | 7.6.<br>7.6. |                                                       |     |

|   | 7.6.<br>7.6. | · ·                                                   |     |

|   | 7.7          | PSE Power frequency common mode immunity test         |     |

|   | 7.7.         | 1 Test Setup                                          | 46  |

|   | 7.7.         |                                                       |     |

|   | 7.7.         | 3 Report                                              | 47  |

|    | 7.7.4      | Expected Results                                                              | 47 |

|----|------------|-------------------------------------------------------------------------------|----|

| -  | 7.8 PSE    | E voltage verification test in the absence of false ELC3 (Off-hook) detection | 47 |

|    | 7.8.1      | Test Setup                                                                    | 47 |

|    | 7.8.2      | Method of Procedure                                                           | 47 |

|    | 7.8.3      | Report                                                                        | 47 |

|    | 7.8.4      | Expected Results                                                              | 47 |

| -  | 7.9 PSE    | E Micro-interrupt test                                                        |    |

|    | 7.9.1      | Test Setup                                                                    |    |

|    | 7.9.2      | Method of Procedure                                                           |    |

|    | 7.9.3      | Report                                                                        |    |

|    | 7.9.4      | Expected Results                                                              | 48 |

| 8  | DPU sta    | ndalone functional testing                                                    | 49 |

| 8  | 3.1 DPI    | J Signature resistor test                                                     | 49 |

| `  | 8.1.1      | Test Setup                                                                    |    |

|    | 8.1.2      | Method of Procedure                                                           |    |

|    | 8.1.3      | Report                                                                        |    |

|    | 8.1.4      | Expected Results                                                              |    |

| 8  | 3.2 DPI    | J power sharing test                                                          |    |

|    | 8.2.1      | Test Method A                                                                 |    |

|    | 8.2.2      | Test Method B                                                                 | 52 |

| 9  | System     | level RPF tests                                                               | 54 |

| (  | ).1 Sino   | gle Pair Data Rate Test                                                       | 54 |

| •  | 9.1.1      | Purpose                                                                       |    |

| Ар | pendix I.  | DPU Emulator for PSE standalone testing                                       |    |

| Ар | pendix II. | Differential Mode RPF Noise Limits test                                       | 57 |

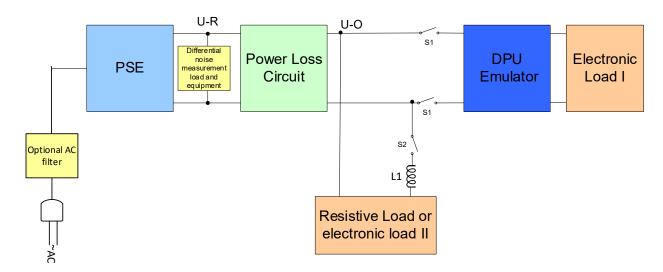

| ı  | I.1 Tes    | t Purpose                                                                     | 57 |

|    |            | t Setup                                                                       |    |

|    |            | hod of Procedure                                                              |    |

|    | I.4 Rep    | oort                                                                          | 58 |

|    |            | ected Results                                                                 |    |

|    |            |                                                                               |    |

# **List of Figures**

| Figure 5-1 – Functional reference model of the reversely powered DPU in a typical FTTdp deployn | nent |

|-------------------------------------------------------------------------------------------------|------|

|                                                                                                 | 15   |

| Figure 6-1 – Test setup for PSE electrical compliance and DPU signature detection and power     |      |

| classification                                                                                  | 17   |

| Figure 6-2 – Test setup for PSE tests in presence of faults                                     |      |

| Figure 6-3 – Test setup for compliance of PSE startup in presence of MELT signature             |      |

| Figure 6-4 – Test setup for PSE tests in presence of off-hook phone emulator                    |      |

| Figure 6-5 – Test setup for PSE power class with DPU power signature defined as a pulse impulse |      |

| Figure 6-6 – DPU Signature circuit                                                              |      |

| Figure 6-7 – Electronic Load (I <sub>SRi</sub> ) increments                                     |      |

| Figure 6-8 – ELC reference diagram                                                              | 21   |

| Figure 6-9 – Resistive network for power loss circuit                                           | 23   |

| Figure 6-10 – Off-hook emulator circuitry                                                       | 24   |

| Figure 6-11 – Test setup for PSE voltage verification in the absence of false ELC3 detection    | 25   |

| Figure 6-12 – Line currents and the timing diagram of the MOSFETs                               | 27   |

| Figure 6-13 – Test setup for DPU power sharing testing                                          |      |

| Figure 6-14 – Power loss circuit with shunt resistor                                            |      |

| Figure 6-15 – Power Test setup for DPU Signature resistor test                                  | 29   |

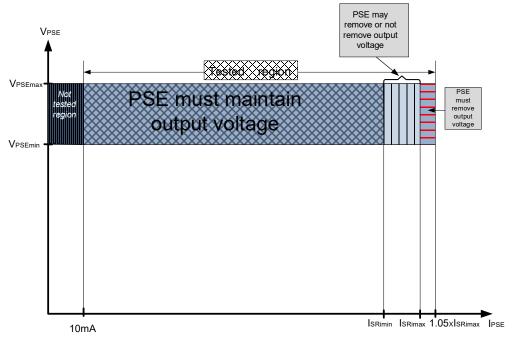

| Figure 7-1 – Allowed tested region for V <sub>PSE</sub> -I <sub>PSE</sub> diagram               |      |

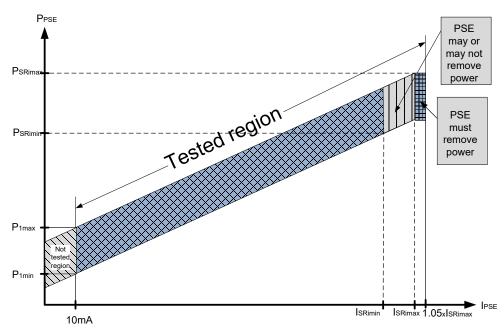

| Figure 7-2 – Allowed tested region for P <sub>PSE</sub> -I <sub>PSE</sub> diagram               |      |

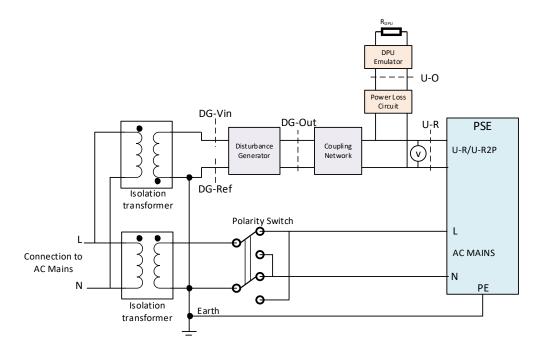

| Figure 7-3 – Power Frequency Common Mode Immunity test setup                                    | 45   |

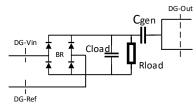

| Figure 7-4 – Disturbance Generator for Power Frequency Common Mode Immunity test                | 46   |

| Figure 7-5 – Coupling for Power Frequency Common Mode Immunity test                             |      |

| Figure 7-6 – Example of a test setup for PSE micro-interrupt test                               |      |

| Figure 10-1 – DPU Emulator for PSE standalone testing (example)                                 |      |

|                                                                                                 |      |

# **List of Tables**

| Table 5-1 – DPU Information                                                           | 16 |

|---------------------------------------------------------------------------------------|----|

| Table 5-2 – CPE Information                                                           | 16 |

| Table 5-3 – RPF Information                                                           |    |

| Table 6-1 – Valid parameter values for signature circuit                              | 19 |

| Table 6-2 – Non-valid parameter values for signature circuit                          | 19 |

| Table 6-3 – Power Classification signature                                            | 20 |

| Table 6-4 – RPF Power Class detection                                                 | 20 |

| Table 6-5 – Error Line Condition Parameters and Detection Criteria                    | 22 |

| Table 6-6 - Upper limits of the Off-hook phone DC voltage/current characteristics     | 22 |

| Table 6-7 – R <sub>loop</sub> values for power loss circuit                           | 23 |

| Table 6-8 – MELT signatures                                                           | 23 |

| Table 6-9 – Off-hook emulator components                                              | 25 |

| Table 6-10 – Test setup components                                                    | 25 |

| Table 6-11 – Test setup state definition and timing specification                     |    |

| Table 6-12 – Temperature and Humidity Range of Test Facility                          | 30 |

| Table 6-13 – AC voltage measurements of Test Facility                                 |    |

| Table 7-1 – PSE electrical specification on U-R interface                             | 38 |

| Table 7-2 – Component specification of the Disturbance generator and coupling circuit | 46 |

| Table 8-1 – Power supplies specification                                              |    |

| Table 8-2 – Current and voltage meters specifications                                 |    |

| Table 8-3 – Loop Resistances for DPU standalone power sharing test                    | 50 |

| Table 9-1 – Single line performance loop requirements for locally powered DPU         | 55 |

# **Executive Summary**

Broadband Forum's Technical Report TR-338 [1] defines functional and safety test cases for the Power Source Equipment (PSE) implemented according to ETSI specification TS 101 548-1 [3], either as a stand-alone device or as a function integrated in the G.fast network termination ([4] and [5]), and reversely powered DPU implementations ([1]).

Issue 1 of TR-338 focuses on a PSE standalone tests in the test setup in which a DPU implementation only includes the reverse powering features specified in [3].

Amendment 1 to TR-338 includes new Appendix, with testing guidance and generalized test setup for the Differential Mode RPF Noise Limits test.

Issue 2 of this Technical Report integrates TR-338 Amendment 1, and expands on the test cases defined in issue 1 through the addition of:

- a. PSE Touch current test

- b. PSE Power frequency common mode immunity test

- c. PSE voltage verification test in the absence of false ELC3 (Off-hook) detection

- d. PSE Micro-interrupt test

- e. DPU Signature resistor test

- f. DPU power sharing test

- g. System level RPF tests

# 1 Purpose and Scope

# 1.1 Purpose

With short copper loops required by G.fast Distribution Point Units (DPUs) that push the deployment of the DPUs closer to the customer premises, local power and forward power may not be available at the deployment location. To power the DPU, power will come from the customer premises location over the copper pair used for data transmission; this is referred to as Reverse Power Feed (RPF).

Broadband Forum's technical Report TR-338 [1] specifies a set of test cases and related pass/fail requirements for reverse powering (RPF) of remote network nodes (Gfast DPUs, single-port or multiport) from customer premises equipment (one or multiple CPEs). Specifically, it defines functional and safety test cases for the Power Source Equipment (PSE) implemented according to ETSI specification TS 101 548-1 [3], either as a stand-alone device or as a function integrated in the G.fast (G.9700 [4] and G.9701 [5]) network termination ([5] and [5]), and reversely powered DPU implementations ([1]).

Issue 1 of TR-338 focuses on PSE standalone tests in the test setup in which a DPU implementation only includes the reverse powering features specified in [3].

Issue 2 of this Technical Report integrates TR-338 Amendment 1, and expands on the test cases defined in issue 1 through the addition of:

- a. PSE Touch current test

- b. PSE Power frequency common mode immunity test

- c. PSE voltage verification test in the absence of false ELC3 (Off-hook) detection

- d. PSE Micro-interrupt test

- e. DPU Signature resistor test

- f. DPU power sharing test

- g. System level RPF tests

Test cases are mainly specified with reference to ETSI TS 101 548-1 [3] and TR-301 Issue 2 [1] requirements. Furthermore they are designed to ensure safe deployment of RPF equipment.

# 1.2 Scope

This document is the next revision of TR-338 [1].

August 2020

# 2 References and Terminology

# 2.1 Conventions

In this Technical Report, several words are used to signify the requirements of the specification. These words are always capitalized. More information can be found be in RFC 2119 [8].

**SHALL** This word, or the term "REQUIRED", means that the definition is an absolute requirement of the specification. **SHALL NOT** This phrase means that the definition is an absolute prohibition of the specification. SHOULD This word, or the term "RECOMMENDED", means that there could exist valid reasons in particular circumstances to ignore this item, but the full implications need to be understood and carefully weighed before choosing a different course. SHOULD NOT This phrase, or the phrase "NOT RECOMMENDED" means that there could exist valid reasons in particular circumstances when the particular behavior is acceptable or even useful, but the full implications need to be understood and the case carefully weighed before implementing any behavior described with this label. This word, or the term "OPTIONAL", means that this item is one of an **MAY** allowed set of alternatives. An implementation that does not include this option MUST be prepared to inter-operate with another implementation that does include the option.

#### 2.2 References

The following references are of relevance to this Technical Report. At the time of publication, the editions indicated were valid. All references are subject to revision; users of this Technical Report are therefore encouraged to investigate the possibility of applying the most recent edition of the references listed below.

A list of currently valid Broadband Forum Technical Reports is published at <a href="https://www.broadband-forum.org">www.broadband-forum.org</a>.

| Document                   | Title                                                                                                      | Source | Year     |

|----------------------------|------------------------------------------------------------------------------------------------------------|--------|----------|

| [1] TR-338<br>Issue 1      | Reverse Power Feed Testing                                                                                 | BBF    | 2018     |

| [2] TR-301<br>Issue 2      | Architecture and Requirements for Fiber to the Distribution Point                                          | BBF    | 2017     |

| [3] TS 101 548-1<br>v2.4.1 | European Requirements for Reverse Powering of<br>Remote Access Equipment; Part 1: Twisted pair<br>Networks | ETSI   | 2020     |

| [4] G.9700                 | Fast Access to Subscriber Terminals (G.fast) –<br>Power spectrum density specification                     | ITU-T  | 2018     |

| [5] G.9701                 | Fast Access to Subscriber Terminals (G.fast) –<br>Physical layer specification                             | ITU-T  | 2018     |

| [6] G.997.2                | Physical layer management for G.fast transceivers (2018)                                                   | ITU-T  | 2019     |

| [7] TR-380                 | G.fast Performance Test Plan                                                                               | BBF    | 2020     |

| [8] RFC 2119               | Key words for use in RFCs to Indicate Requirement                                                          | IETF   | 1997     |

| August 2020                | © The Broadband Forum. All rights reserved                                                                 |        | 10 of 58 |

Levels

#### 2.3 Definitions

The following terminology is used throughout this Technical Report.

Gfast Marketing term for G.fast

Mains Supply AC electricity power supply

Normal operation State of a system (i.e., a DPU reversely powered by a PSE) reached after the

start-up procedure has been completed

Start-up operation

Start-up procedure of a system (powering part of a DPU and PSE)

**POTS Remote**

Copper

Reconfiguration

(RCR)

RCR refers to the Scenario where POTS from the exchange may be provided to the subscriber and shall be disconnected by the DPU, prior to start-up of the DPU. This is an optional extension of the MDSU protocol on lines where POTS may be present. Refer to clause 6.2.5.1 in [3].

One-box solution Power Source Equipment (PSE) is integrated in the same physical entity as

CPE

Two-box solution Power Source Equipment (PSE) is a stand-alone device and not integrated in

the same physical entity as CPÉ

PoE Power over Ethernet describes any of several standards (IEEE 802.3) which

pass electric power along with data on twisted pair Ethernet cabling

PoE PD PoE Powered Device

#### 2.4 Abbreviations

This Technical Report uses the following abbreviations:

AC Alternating Current

CPE Customer Premises Equipment

Note: CPE is also referred to as NTE (see [3])

CPE ME CPE Management Entity

DC Direct Current

ELC Error Line Condition

DPU Distribution Point Unit

DPU ME DPU Management Entity

FTTdp Fiber to the distribution point

FTU G.fast Transceiver Unit

FTU-O FTU at the Optical Network Unit (i.e., operator end of the line)

FTU-R FTU at the Remote site (i.e., subscriber end of the line)

G.fast Fast Access to Subscriber Terminals

MDSU Metallic Detection Start-Up

MELT Metallic Line Testing

NMS Network Management System

NT Network Termination

PRP Protocol for RCR

PE Power Extractor

PHY-L Physical Layer

POTS Plain Old Telephone Service

PS Power Splitter

PSE Power Source Equipment

PSU Power Supply Unit

RCR Remote Copper Reconfiguration

RPF Reverse Power Feed SUT System Under Test

UPS Un-interruptible Power Supply

# 3 Technical Report Impact

# 3.1 Energy Efficiency

TR-338 has no impact on energy efficiency.

# 3.2 Security

TR-338 has no impact on security.

# 3.3 Privacy

Any issues regarding privacy are not affected by TR-338.

# 4 Common Test Information

# 4.1 Compliance Requirements

The tests contained in this document are intended to verify that a Power Source Equipment (PSE) complies with the functional i.e., powering, electrical and safety requirements of ETSI technical specification TS 101 548 [3].

# 4.2 Test Plan Passing Criteria

The tests contained in this document are each marked with a test status, indicating: "mandatory", "conditional mandatory" or "optional."

Tests marked as "mandatory" SHALL be performed when completing testing according to this test plan.

Tests marked as "conditional mandatory" also include a conditional statement; which if met, indicates the test SHALL be considered as "mandatory." If the conditional statement is not met, the test SHALL be considered as "not applicable."

Tests marked as "optional" MAY be completed at the request of the tester or equipment manufacturer. For the purpose of determining a summary result, such as indicating a device "passes TR-338 testing," the device SHALL pass all "mandatory" tests and all applicable "conditional mandatory" tests. "Optional" tests SHALL not impact the summary result.

# **5 Equipment Features**

# 5.1 System Information

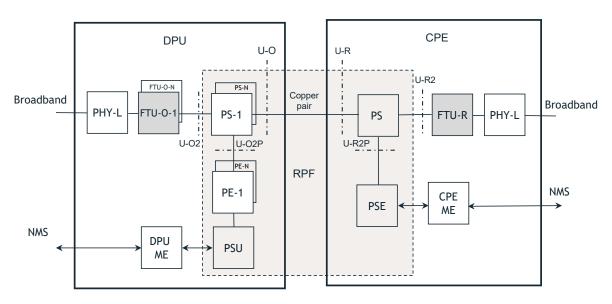

Figure 5-1 illustrates the functional reference model of the reversely powered DPU in a typical FTTdp deployment. The main functional blocks DPU, CPE and the reverse power feed system (RPF) are shown for line 1 of N lines connected to a DPU.

Figure 5-1 – Functional reference model of the reversely powered DPU in a typical FTTdp deployment

The FTU-O is located inside the distribution point unit (DPU) at the network side of the wire-pair (U-O reference point). The FTU-R is located at the customer premises side of the wire-pair (U-R reference point). The management of a DPU and CPE is performed by the network management system (NMS), passing management information to each management entity (DPU ME and CPE ME). The PHY-L blocks represent the physical layer of the DPU towards the access network and of the NT towards the customer premises, and the layer 2 and above functionalities contained in the DPU and the NT. The power is inserted on the line by the Power Source Equipment (PSE) located in the customer premises and extracted from the line by the Power Extractor (PE) located in the DPU. Power is extracted from each active port and combined in the Power Supply Unit (PSU). The PE and PSU are separated from the broadband signal on the line (at reference point U-O and U-R) by a power splitter (PS).

The DPU SHALL support the DPU-northbound management protocol that allows the ability to configure and retrieve the G.997.2 [6] managed objects used in this test plan. The management protocol is vendor discretionary.

The CPE is managed through the DPU-MIB and the G.9701 initialization/eoc/RMC. No LAN-side management protocol is required for the execution of this test plan, except as required to configure the CPE to pass Ethernet traffic between the G.fast and LAN interface(s).

In case of a 1-box solution where the PSE is in the same physical entity as the CPE, the RPF indications and OAM parameters shall be exchanged between the CPE ME and DPU ME using the G.997.2 RPF OAM management protocol. Otherwise, in case of a 2-box solution, ETSI TS 101 548 specification provides the foundation for the RPF parameters and indications that are exchanged between the PSE and the DPU.

Table 5-1, Table 5-2, and Table 5-3 are intended to provide test engineers and readers of the test report with sufficient information about the system (DPU, CPE and RPF) in order to ensure repeatability of results and to allow for accurate comparisons of reported test results. The tables

SHALL be populated prior to the start of the testing and SHALL be included as part of the test report. All fields SHALL be populated; if an item is not applicable, the item MAY be marked as "Not Applicable".

# **Table 5-1 – DPU Information**

| Parameter                                                              | Reference section in G.997.2 |

|------------------------------------------------------------------------|------------------------------|

| DPU system vendor ID (DPU_SYSTEM_VENDOR)                               | 7.13.2.1                     |

| DPU system serial number (DPU_SYSTEM_SERIALNR)                         | 7.13.2.3                     |

| FTU O ITU-T G.994.1 vendor ID (FTUO_GHS_VENDOR)                        | 7.13.1.1                     |

| FTU O version number (FTUO_VERSION)                                    | 7.13.1.3                     |

| Support of POTS Remote copper reconfiguration Protocol (PRP)           | A.6.2.7                      |

| Maximum DPU reach resistance Rreach,dpu (7.5.2.1 of [ETSI TS 101 548]) |                              |

| DPU power class (SR1, SR2 or SR3) (7.2 of [ETSI TS 101 548])           |                              |

| Total number of ports (N)                                              |                              |

# **Table 5-2 – CPE Information**

| Parameter                                       | Reference section in G.997.2 |

|-------------------------------------------------|------------------------------|

| NT system vendor ID (NT_SYSTEM_VENDOR)          | 7.13.2.2                     |

| NT system serial number (NT_SYSTEM_SERIALNR)    | 7.13.2.4                     |

| FTU R ITU-T G.994.1 vendor ID (FTUR_GHS_VENDOR) | 7.13.1.2                     |

| FTU R version number (FTUR_VERSION)             | 7.13.1.4                     |

# Table 5-3 - RPF Information

| Parameter                                                          | Reference section in G.997.2 |

|--------------------------------------------------------------------|------------------------------|

| PSE in the same physical entity with CPE (1-box solution)          | A.7.6.2.1                    |

| PSE Product Name/Model if not integrated with CPE (2-box solution) |                              |

| PSE power class (SR1, SR2 or SR3) (7.2 of [ETSI TS 101 548])       |                              |

| Battery backup available at the PSE                                | A.7.6.2.2                    |

| Support of POTS Remote copper reconfiguration Protocol (PRP)       | A.7.6.2.3                    |

| Power splitter (external) Product Name/Model                       |                              |

# 6 Test Environments

# 6.1 Test setup

This section specifies the test setups applicable to this Test Plan.

# 6.1.1 Test setup for PSE functional testing

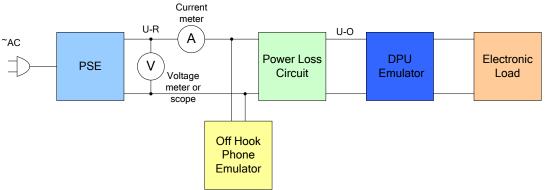

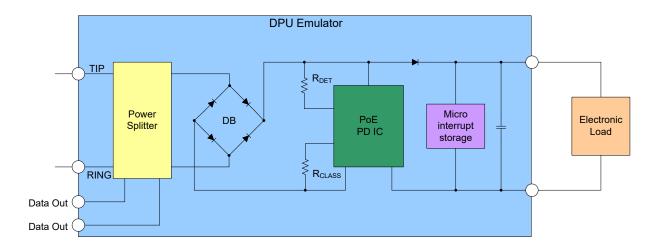

In this test plan the Gfast DPU is replaced by a DPU emulator.

The test setups below contain a number of circuits (e.g., DPU signature and power classification, etc.) and test instruments (e.g., voltage and current meter, electronic load). Details about these elements are provided in the sections below. Figures show only the case of a PSE with internal power splitter and the related interface named U-R. The voltage and current meter shown in the test setups below have time domain measurement capabilities.

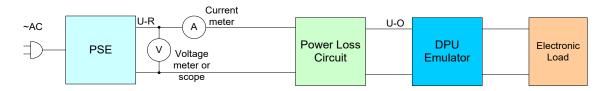

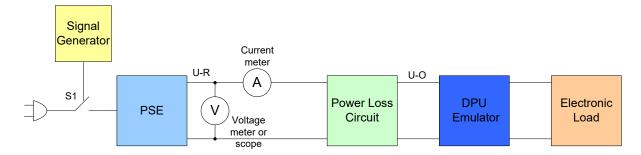

Figure 6-1 shows the test configuration for PSE compliance tests to the electrical characteristics of short range power classes of ETSI TS 101 548 [3] and tests for the DPU signature detection and RPF power classification.

This configuration comprises an emulated DPU RPF front-end which includes the DPU Signature detection and RPF Power Classification circuits. These circuits are designed to operate over lower voltage ranges than nominal RPF voltage, not overlapped between each other.

The following describes the basic theory of operation of the RPF systems and is intended to aid the reader in understanding the purpose of the test setup(s). All values are provided for information purposes only, and the reader is encouraged to refer to the ETSI TS 101 548 [3] for the normative values.

The PSE performs fault detection first; if no fault is detected then it proceeds to the signature detection phase.

Then the PSE performs the DPU signature detection first (over a 2.8V-10V range) and the DPU disconnects the resistor signature if the voltage is larger than 10.1V - 12.8V.

Then the PSE performs the power classification (over a 14.5V - 20.5V range on the DPU side) and if the expected RPF Power Classification circuit (i.e., the expected  $I_{CLASS}$ ) is detected the PSE increases the voltage and the power classification circuit is disconnected. Only after these two recognition phases are completed the PSE increases the voltage up to its steady-state value.

The DPU Signature circuit and the RPF Power Classification circuit are specified in sections 6.1.1.1 and 6.1.1.2 respectively. The behavior of the Electronic Load for a proper execution of the test for PSE characterization is described in section 6.1.1.3.

Figure 6-1 through Figure 6-3 below show only the PSE, regardless of this being a stand-alone device or a function integrated with a NT Module/CPE. Furthermore the powering of the PSE (i.e., mains supply or battery supply) is not shown.

Figure 6-1 – Test setup for PSE electrical compliance and DPU signature detection and power classification

Figure 6-1shows a simplified schematic of PSE test setup using an electronic load as the load termination. For electronic loads, the desired output current SHOULD be adjusted in constant current mode.

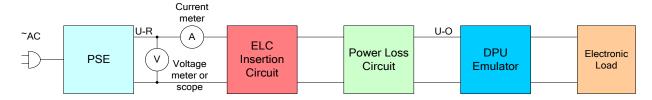

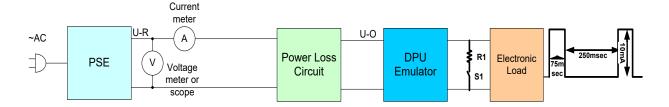

Figure 6-2 shows the test configuration for PSE tests involving fault conditions (e.g., startup with/without fault conditions, fault detection during normal PSE and DPU operation). The power class of the PSE and of the DPU (as implemented in its Power Classification circuit) shall match together [3].

The ELC (i.e., fault or Error Line Condition) insertion and Power Loss circuit are specified in sections 6.1.1.4 and 6.1.1.5 respectively.

Figure 6-2 – Test setup for PSE tests in presence of faults

The setup in Figure 6-2 requires the ability to collect a time domain measurement of the voltage and current on the line. For example this could be implemented via an oscilloscope with two channels used to measure the  $V_{DC}$  (through a differential probe) and the  $I_{DC}$  (through a differential probe) with a triggered measurement start.

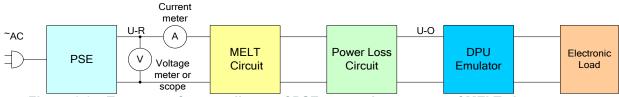

Figure 6-3 shows the test setup for compliance of the PSE startup in the presence of MELT signature. The MELT signature is defined in section 6.1.1.6.

Figure 6-3 – Test setup for compliance of PSE startup in presence of MELT signature

Figure 6-4 shows the test setup for testing PSE detection of the off-hook phone during startup and normal operation.

Figure 6-4 – Test setup for PSE tests in presence of off-hook phone emulator

Figure 6-5 shows the test setup for testing PSE power class with DPU power signature defined as a pulse current with amplitude 10mA, pulse duration 75ms and period 325ms.

Figure 6-5 – Test setup for PSE power class with DPU power signature defined as a pulse impulse

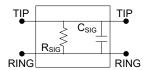

# 6.1.1.1 DPU Signature circuit

The DPU Signature circuit emulates the one implemented in a DPU and it is shown in Figure 6-6. A mechanical or solid-state switch shall be located in series with the signature circuit and it has to be controlled such that the signature circuit is applied or removed during the appropriate phases of the start-up protocol. An example of a control circuit can be found in Appendix A.

Figure 6-6 - DPU Signature circuit

The valid signature values specified in ETSI TS 101 548 [3] are reported in Table 6-1.

Table 6-1 - Valid parameter values for signature circuit

|  |                   |         | 0       |

|--|-------------------|---------|---------|

|  | Symbol            | Min     | Max     |

|  | $R_{V-SIG}$       | 23.7 kΩ | 25.5 kΩ |

|  | $C_{V	ext{-}SIG}$ | 50 nF   | 120 nF  |

ETSI TS 101 548 [3] specifies also non-valid signature values. These are reported in Table 6-2.

Table 6-2 – Non-valid parameter values for signature circuit

| Symbol              | Low   | High  |

|---------------------|-------|-------|

| R <sub>NV-SIG</sub> | 15 kΩ | 33 kΩ |

| $C_{NV	ext{-SIG}}$  | 10 μF |       |

## 6.1.1.2 RPF Power Classification circuit

In addition to the detection signature, the DPU includes a power classification signature. The key objectives for the classification circuitry are the following:

- Establish mutual identification of PSE and DPU as enhanced validation mechanism on top of the detection mechanism. This addresses the scenario in which a combination of connected equipment (e.g., phones, fax machines, etc.) would have the same signature as those of a valid DPU.

- Provide power levels interoperability criteria between PSE power classes and DPU power consumption

During the power classification phase, the DPU SHALL present only one power classification signature ( $V_{\text{CLASS}}$ ,  $I_{\text{CLASS}}$ ) according to Table 6-3. A mechanical or solid-state switch shall be located in

series with the classification signature and it has to be controlled such that the classification signature is applied or removed during the appropriate phases of the start-up protocol. An example of a control circuit can be found in 7.9.1.

Table 6-3 - Power Classification signature

| Power classification signature | Voltage V <sub>CLASS</sub> at DPU | Current I <sub>CLASS</sub> (min) | Current I <sub>CLASS</sub> (max) |

|--------------------------------|-----------------------------------|----------------------------------|----------------------------------|

| Class SR1                      |                                   | 9 mA                             | 12 mA                            |

| Class SR2                      | 14.5V to 20.5V                    | 17 mA                            | 20 mA                            |

| Class SR3                      |                                   | 26 mA                            | 30 mA                            |

During the power classification phase, the PSE SHALL apply the voltage ( $V_{CLASS\_PSE}$ ) between 16.5V and 20.5V (section 6.2.2 in [3]) and detect the RPF Power Class based on the measured current ( $I_{CLASS\_MEAS}$ ) according to Table 6-4.

Table 6-4 - RPF Power Class detection

| RPF power class | Voltage V <sub>CLASS_PSE</sub> at PSE | Current<br>I <sub>CLASS_MEAS</sub><br>(min) | Current<br>I <sub>CLASS_MEAS</sub> (max) |

|-----------------|---------------------------------------|---------------------------------------------|------------------------------------------|

| RPF SR1         |                                       | 8 mA                                        | 13 mA                                    |

| RPF SR2         | 16.5V to 20.5V                        | 16 mA                                       | 21 mA                                    |

| RPF SR3         |                                       | 25 mA                                       | 31 mA                                    |

# 6.1.1.3 Electronic Load

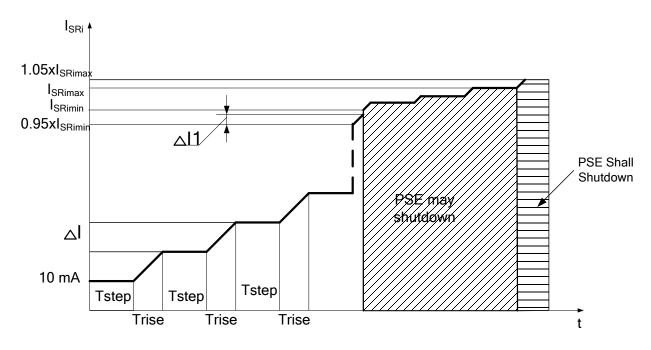

The Electronic Load circuit should apply the load according to Figure 6-7:

- In 3% increments of  $I_{SRimax}$ , from 10mA to 0.95% ×  $I_{SRimin}$

- $\circ$   $\Delta I = 5mA for SR1$

- $\circ$   $\Delta I = 7.5 \text{mA for SR2}$

- $\circ$   $\Delta I = 10.5 \text{mA} \text{ for SR3}$

- In 2mA increments from 0.95×I<sub>SRimin</sub> to 1.05×I<sub>SRimax</sub>

- Step time T<sub>STEP</sub> = ≥30ms

**Note:** If measurements are performed manually,  $T_{\text{STEP}}$  could be increased to allow manual measurements of voltage, current, and power.

Rise time T<sub>RISE</sub> = 20ms

Note: The rate of change of current shall not exceed 1mA/µs (Table 37 in [3]).

Figure 6-7 – Electronic Load (I<sub>SRi</sub>) increments

# 6.1.1.4 Error Line Condition (ELC) circuit

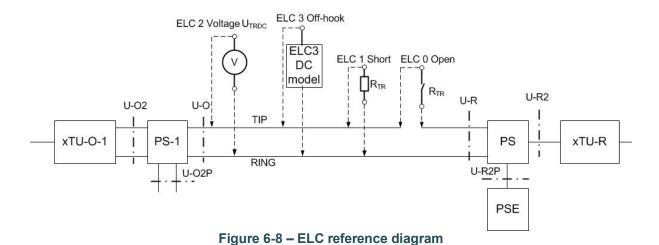

The equivalent network model of the above Error Line Condition (ELC) circuit shown in Figure 6-8 is defined in section 6.1.1 in [3]. In practical implementations all ELC functions (Fig 6-7, Fig 6-2, Fig 6-4) MAY be combined into a single test setup.

The Error Line Condition parameters and detection criteria for the ELC network model are defined in Table 6-5.

**Error Line Condition Detection Criteria** Description **Parameter**  $R_{Emin} = 1 M\Omega$  $R_{TR} \ge R_{Emin}$  for a duration exceeding 300ms (see  $C_{\text{Emax}} = 100 \text{ nF}$ ELC<sub>0</sub> Open tip-to-ring NOTE 1)  $C_{TR} \le C_{Emax}$ ELC1 Short tip-to-ring  $R_{Emax} = 140 \Omega$  $R_{TR} \le R_{Emax}$ POTS Exchange U<sub>TRDCEmax</sub>= 3 V |U<sub>TRDC</sub>| ≥ U<sub>TRDCEmax</sub> ELC2 (foreign) DC voltage Measured voltage and current in the range ELC3 Off-hook phone below the upper limit of the DC characteristics defined in Table 6-6.

Table 6-5 - Error Line Condition Parameters and Detection Criteria

**Note 1:** This duration is set such that the definition of ELC0 does not overlap with the Maintain Power Signature definition as defined in Note 4 of Table 41 in [3].

**Note 2:** Due to the definition of parameters, definite detection of ELC1 or ELC3 may be ambiguous.

Feed resistance of ELC2 voltage source SHALL be  $500\Omega$ .

The off-hook phone emulator circuit of Figure 6-9 may be used to implement the ELC3 condition.

The upper limits of the off-hook phone DC characteristics in Table 6-6 are specified in Table 9 in [3].

Table 6-6 - Upper limits of the Off-hook phone DC voltage/current characteristics

| Point | Voltage (V) | Current (mA) |

|-------|-------------|--------------|

| Α     | 9           | 0            |

| В     | 9           | 20           |

| С     | 14.5        | 42           |

| D     | 40          | 50           |

| Е     | 60          | 56           |

NOTE: Linear interpolation of voltage in function of current shall be used to obtain values between points A-E.

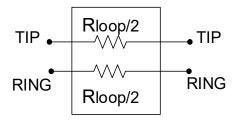

# 6.1.1.5 Power Loss Circuit

This section specifies the Power Loss circuit used to model a loop resistance  $R_{loop}$ , which is defined as the total DC resistance measured between the two conductors at one reference point while shorting the other two conductors at the other reference point:

- Loop resistance between U-O and U-RP2 is illustrated in Figure 29 [3]

- Loop resistance between U-O and U-R is illustrated in Figure 30 [3]

Loop resistance shall be implemented via a resistive network with fixed or tunable resistances at DC expressed in  $\Omega$ s. This resistive value includes the copper loop resistance and any additional resistance between the above interfaces (e.g., a connector, over-current protectors, a power splitter). The resistive circuit is shown in Figure 6-9.

Figure 6-9 – Resistive network for power loss circuit

The  $R_{loop}$  values for the power loss circuit of are listed in Table 6-7. These values roughly represent 20, 50, 100, 200, and 250 m loop lengths of cable with a loop resistance of 0.168 $\Omega$ /m (0.5 mm section).

Table 6-7 - R<sub>loop</sub> values for power loss circuit

| 100 |               |

|-----|---------------|

|     | Nominal value |

| R1  | 4Ω ± 5 %      |

| R2  | 8Ω ± 5 %      |

| R3  | 16Ω ± 5 %     |

| R4  | 34Ω ± 5 %     |

| R5  | 43Ω ± 5 %     |

# 6.1.1.6 MELT signature

MELT signatures located at the U-R interface are defined in section 6.1.2 in [3].

Table 6-8 - MELT signatures

|   |                                   | MELT signatur                                                                                                     | Comments                                                                          |  |                                     |

|---|-----------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|--|-------------------------------------|

| 1 | D R                               | Component R U <sub>F(D)</sub>                                                                                     | Nominal value<br>470kΩ+/-1%<br>0.7V (at I <sub>f</sub> =10mA) +/- 0.1V            |  | DR type<br>Specified in TR-<br>286  |

| 2 | D <sub>1</sub> D <sub>2</sub> R C | $ \begin{array}{c} \text{Component} \\ \text{R} \\ \text{C} \\ \text{U}_{Z(D1)} \\ \text{U}_{Z(D2)} \end{array} $ | Nominal value  100kΩ +/- 1%  470nF +/- 1%  6.8V +/- 5% @ 50μA  6.8V +/- 5% @ 50μA |  | ZRC type<br>Specified in TR-<br>286 |

| 3 | 1                   |                                                                                                                                               |                         |  | RC type |

|---|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|---------|

|   | R                   | Component                                                                                                                                     | Nominal value           |  |         |

|   |                     | R                                                                                                                                             | 20kΩ +/- 1%             |  |         |

|   | $\parallel$ $\pm$ c | С                                                                                                                                             | 2.2µF +/- 10%           |  |         |

|   | '                   | NOTE 1: time co                                                                                                                               | onstant t = R×C ≤ 49ms. |  |         |

|   |                     | NOTE 2: additional constraint for PSE supporting POTS Remote copper reconfiguration Protocol (PRP) is a resistive part exceeding $4k\Omega$ . |                         |  |         |

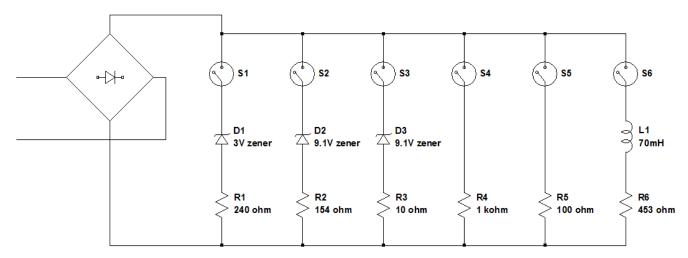

# 6.1.1.7 Off-hook phone emulator circuitry

This section specifies an off-hook phone emulator circuit which shall be used for testing the PSE detection of the off-hook phone. The purpose of this circuit is to emulate off-hook phone detection on a PSE startup and powering mode and meet requirements for off-hook phone specification according to ETSI TS101 548 Table 9, and take into account Table 37 (Note 5).

The off-hook emulator circuitry is presented in Figure 6-10.

Figure 6-10 – Off-hook emulator circuitry

Purpose of switches S1 to S5 is to emulate the off-hook phone behavior during different phases of RPF PSE operations: detection, classification and normal operation when PSE is powering DPU according to the voltage/current characteristics of the off-hook phone defined in Table 6-6.

Off-hook phone behavior during the detection phase of PSE start up at  $I_{S1@9V}$ =19mA and  $I_{S4@9V}$ =7.6 mA is emulated with switches S1 and S4 turned on.

Off-hook phone behavior during the classification phase of PSE start up at  $I_{S2@18V}$ =48.7mA and  $I_{S3@18V}$ =750 mA is emulated with switches S2 and S3 turned on.

Off-hook phone behavior during the normal PSE operation supplying power to DPU at  $I_{S4@57V}$ =55.6mA and  $I_{S5@18V}$ =5.56A is emulated with switches S4 and S5 turned on.

Purpose of switch S6 is to test immunity of the PSE off-hook detection circuitry to load transients below 1mA/µs (Table 37 in [3]).

The off-hook emulator components are listed in Table 6-9.

| Table 6-9 – Of | f-hook emulator components |

|----------------|----------------------------|

| Component      | Nominal value              |

| Component         | Nominal value                 |

|-------------------|-------------------------------|

| BR                | 80V-100V, 5A bridge rectifier |

| D1                | 3V+/-5% Zener diode           |

| D2, D3            | 9.1V+/-5% Zener diode         |

| R1                | 240Ω ± 1 %                    |

| R2                | 154Ω ± 1 %                    |

| R3                | 10Ω ± 1 %                     |

| R4                | 1000Ω ± 1 %                   |

| R5                | 100Ω ± 1 %                    |

| R6                | 453Ω ± 5 % (Note 1)           |

| L1                | 70mH ± 10 % (Note 2, Note 3)  |

| S1,S2,S3,S4,S5,S6 | Toggle switches (Note 4)      |

Note 1: Resistance value of R6 includes the DC resistance of inductor L1.

Note 2: Parasitic capacitance of inductor L1 shall be less than 10pF.

Note 3: Inductor L1 can be replaced by another electronic circuit to limit the dl/dt.

Note 4: Upon closure, the toggle switch shall not limit the dl/dt below 10mA/µs.

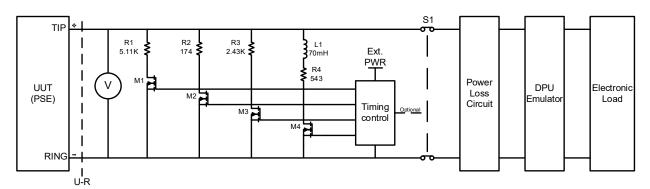

# 6.1.1.8 Test setup for PSE voltage verification in the absence of false ELC3 detection

This section describes the test setup for PSE voltage verification in the absence of false ELC3 detection, according to Note 5 of Table 41 of TS 101 548-1 [3].

The test setup is shown in Figure 6-11.

Figure 6-11 – Test setup for PSE voltage verification in the absence of false ELC3 detection

The test setup components are listed in Table 6-10.

Table 6-10 - Test setup components

| Component | Nominal value |

|-----------|---------------|

| R1        | 5110 Ω +/-1%  |

| R2        | 174 Ω +/-1%   |

| R3        | 2430 Ω +/-1%  |

| R4                                                                     | 543 Ω +/-1%                                                                                |  |  |

|------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|--|--|

| LO                                                                     | 70mH +/-10% (Note 1)                                                                       |  |  |

| M1,M2,M3,M4 (MOSFETs)                                                  | $V_{dsmax}$ =100V, $R_{dson} \le 1\Omega$                                                  |  |  |

| S1                                                                     | Toggle Switch                                                                              |  |  |

| Timing control block                                                   | Vendor discretionary, for example a MCU, a FPGA or a timing circuit on discrete components |  |  |

| Note 1. Parasitic capacitance of the inductor shall be less than 10pF. |                                                                                            |  |  |

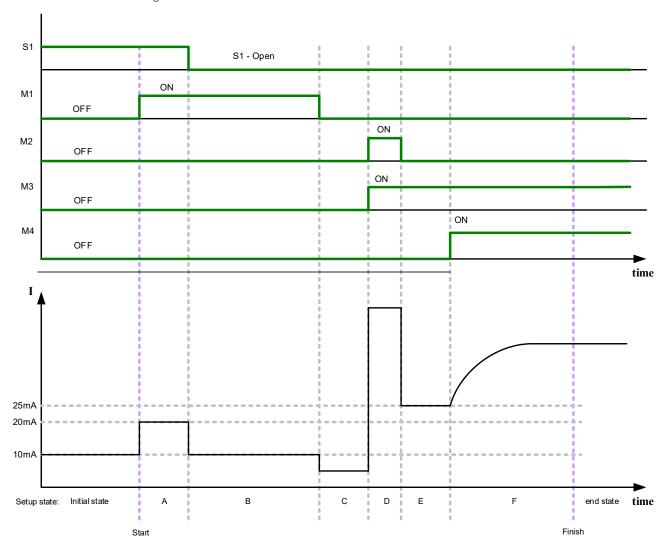

MOSFETs M1, M2, M3 and M4 operate as switches which are controlled by the Timing control block. Switch S1 can be either operated by the timing control block or can be controlled manually. The timing block and the optional manual control shall alter the state of the test setup starting from the Initial state, through A, B, C, D, E, F, till the End state, as defined in Table 6-11.

Table 6-11 – Test setup state definition and timing specification

| Test setup states | Initial | Α      | В    | С      | D      | E      | F    | End  |

|-------------------|---------|--------|------|--------|--------|--------|------|------|

| Duration          | n/a     | t1     | 5s   | 240ms  | 0.5ms  | 4ms    | 5s   | n/a  |

| Applicable notes  |         | Note 1 |      | Note 2 | Note 3 | Note 4 |      |      |

| S1 state:         | closed  | closed | open | open   | open   | open   | open | open |

| M1 state:         | OFF     | ON     | ON   | OFF    | OFF    | OFF    | OFF  | OFF  |

| M2 state:         | OFF     | OFF    | OFF  | OFF    | ON     | OFF    | OFF  | OFF  |

| M3 state:         | OFF     | OFF    | OFF  | OFF    | ON     | ON     | ON   | ON   |

| M4 state:         | OFF     | OFF    | OFF  | OFF    | OFF    | OFF    | ON   | ON   |

Note 1: t1 SHALL be between 1s and 5s.

Note 2: In state C, the line current shall be below 10mA for at least 240ms but no longer than 250ms.

**Note 3:** In state D, the time derivative of the line current shall exceed 1mA/µs after M2 and M3 are closed, and the line current shall be above 25mA but below 373mA for at least 0.5ms but no longer than 1ms.

**Note 4:** In state E, the line current shall be below 25mA for at least 4ms, but no longer than 5ms.

The Line currents and the timing diagram of the MOSFETs M1, M2, M3 and M4 are illustrated in Figure 6-12.

Figure 6-12 – Line currents and the timing diagram of the MOSFETs

# 6.1.2 Test setup for DPU functional testing

# 6.1.2.1 Test setup for DPU power sharing test

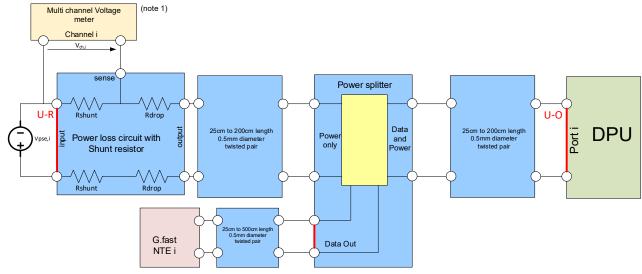

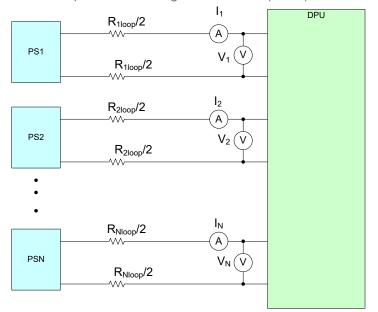

Figure 6-13 shows the test setup for DPU power sharing test. While two test methods, Method A (defined in 8.2.1) and Method B (defined in 8.2.2), are eligible for measuring power extracted by the DPU, multi-channel voltmeter is only used in test Method A.

Votes:

(1) Multi-channel voltage meter is only required when using method A

## Figure 6-13 – Test setup for DPU power sharing testing

The test setup makes use of external power splitters, so that the G.fast signal is separated from the measuring equipment, power loss circuit and voltage source.

When using Method A, the average power at the U-O interface for every port of the DPU is determined by subtracting power loss between U-O and U-R from the injected power at U-R. This is achieved by measuring the loop resistance between U-R and U-O and the voltage at U-R once and sampling the line current periodically for each port of the DPU.

Method B relies on the RPF performance monitoring object "DPU extracted Energy counter (CURR/PREV\_NE\_15\_EE)", as defined in ITU-T G.997.2 [6], to calculate the average power at U-O for every port of the DPU.

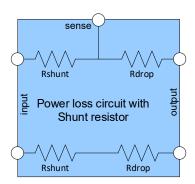

## 6.1.2.1.1 Power loss circuit with Shunt resistor

The Power loss circuit with Shunt resistor is shown in Figure 6-14. It contains two shunt resistors ( $R_{\text{shunt}}$ ) and two fixed or tunable resistors ( $R_{\text{drop}}$ ). One shunt resistor is used by the multi-channel voltmeter to measure the line current. The two fixed or tunable resistors are selected or tuned as such that the loop resistance between U-R and U-O, as defined in clause 7.5.2.1 of TS 101 548-1 [3], for every port of DPU, complies to Table 8-3.

Figure 6-14 - Power loss circuit with shunt resistor

# 6.1.2.1.2 Power splitter

The power splitter shall comply to the "CPE – case 1" power splitter as defined in clause 8.3.5 of TS 101 548-1 [3], whereby:

- The "Power only" interface corresponds to the U-R2P interface of a power splitter

- The "Data and Power" interface corresponds to the U-R interface of a power splitter

- The "Data out" interface corresponds to the U-R2 interface of a power splitter

The power splitter class refers to clause 8.2 of TS 101 548-1 [3] and it shall be defined by the DPU manufacturer.

#### 6.1.2.1.3 G.fast CPE

The G.fast CPE is to be selected by the DPU manufacturer.

# 6.1.2.1.4 Voltage source V<sub>PSE</sub>

The voltage source shall apply a DC voltage between 55.75V and 60V. The output of the voltage source shall be isolated from the earth ground, the isolation shall comply with clause 7.5.1.2 of TS 101 548-1 [3]. The available output power and output impedance shall be ample so that the output voltage shall remain between 55.75V and 60V under any DPU load condition, including inrush current.

To simplify the setup the following is allowed:

- Multiple lines may be fed by a single voltage source

- If multiple voltage sources are used, the negative pole of each voltage source may be interconnected

#### 6.1.2.1.5 Multi-channel voltmeter

The multi-channel voltmeter shall have a least one channel for every port of the DPU. The input impedance of each channel shall exceed  $5M\Omega$ . Filtering or averaging may be applied over the sample acquisition time. The multi-channel voltmeter shall be able to sample at least one channel per second.

# 6.1.2.2 Test setup for DPU Signature resistor test

Figure 6-15 shows the test setup for the DPU Signature resistor (RSIG) test.

Figure 6-15 – Power Test setup for DPU Signature resistor test

# 6.1.3 Test setup for system level RPF testing

# 6.1.3.1 Test Configurations

# 6.1.3.1.1 Ethernet/IP Traffic Setup

See Section 5.1.1 in TR-380.

#### 6.1.3.1.2 Ethernet Traffic Frame Sizes

See Section 5.1.2 in TR-380.

# 6.1.3.1.3 Physical Layer Test Setup

See Section 5.1.3 in TR-380.

# 6.1.3.2 System Under Test (SUT) settings

See Section 5.3 in TR-380.

# 6.1.3.3 Test Loop Topologies

Single line tests (non-vectored) are performed on the TP-100 twisted pair loop type. See Section 5.4.1.1 in TR-380.

# 6.1.3.4 Background Noise

See Section 5.4.2.1 in TR-380.

#### 6.1.3.5 Management of the SUT

See Section 5.4.5 in TR-380.

# 6.1.4 Test Setup characteristics

# 6.1.4.1 Temperature and humidity

The ranges of temperature and humidity of the test facility, over the entire time for which the tests are conducted, SHALL be recorded in a manner similar to that shown in Table 6-12 and SHALL be included as part of the test report.

The measured temperatures and humidities SHOULD be within the acceptable ranges below:

- temperature: between 15°C (59°F) and 35°C (95°F)

- humidity: between 5% and 85%

Table 6-12 - Temperature and Humidity Range of Test Facility

| Parameter   | High | Low |

|-------------|------|-----|

| Temperature |      |     |

| Humidity    |      |     |

# **6.1.4.2 AC voltage**

The AC voltage used to power the PSEs SHALL be recorded as shown in Table 6-13 and included in the test report.

Voltage measurements SHALL be performed three times over the entire time tests are conducted; and, in case of testing of a multi-line DPU, the voltage measurements SHALL be taken over three of the power sources to which the PSEs are connected.

Table 6-13 - AC voltage measurements of Test Facility

| Parameter                                          | Begin test session | Middle test session | End test session |  |

|----------------------------------------------------|--------------------|---------------------|------------------|--|

| AC voltage-1                                       |                    |                     |                  |  |

| AC voltage-2 (NOTE)                                |                    |                     |                  |  |

| AC voltage-3 (NOTE)                                |                    |                     |                  |  |

| Note: This applies only to multi-line DPU testing. |                    |                     |                  |  |

The measured AC voltages SHOULD be within the acceptable ranges below depending on the region the PSE is tested for:

Europe: 230Vac ± 10% @50Hz

North America: 120Vac ± 10% @60Hz

• China: 220Vac ± 10% @50Hz

Japan: 100Vac ± 10% @50Hz or 60Hz

# 7 PSE standalone functional testing

Purpose of this testing is to verify that a Power Source Equipment (PSE) implementation complies with the ETSITS 101 548 [3] requirements. Section 7 specifies functional and safety test cases for the PSE standalone test setup.

Test cases include test procedures and pass/fail requirements for different stages of PSE operation: in presence of error line conditions, during start-up and in normal operation (i.e., steady state when PSE reversely powers a DPU). These tests are applicable to the one-box and two-box solutions.

An example of a DPU emulator is given in 7.9.1.

# 7.1 ELC testing during start-up

The purpose of this test is to verify that a PSE performs detection and protection functions during start up in presence of the following error line conditions (ELC):

- ELC0 open circuit between tip and ring

- ELC1 short circuit between tip and ring

- ELC2 foreign voltage

- ELC3 off-hook phone model

# 7.1.1 ELC0- open tip-to-ring test

Test requirement: Mandatory.

# 7.1.1.1 Test Setup

- 1. The PSE and the DPU emulator SHALL be connected to the test setup shown in Figure 6-2.

- 2. The ELC insertion circuit SHALL be set to ELC0, see Figure 6-8 and Table 6-5.

- 3. The loop resistor  $R_{loop}$  SHALL be set to 43 $\Omega$  +/-5%, see Table 6-7.

- 4. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 5. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 6. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

#### 7.1.1.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait 5 seconds, then measure output voltage at the PSE.

- 3. Disconnect the PSE from the test setup.

- 4. Create the ELC0 condition.

- 5. Reconnect the PSE to the test setup.

- 6. Wait 5 seconds, then measure the output voltage over a 5 second period at the PSE. Record the peak value during this period.

- 7. Record if the device indicated an ELC0 failure condition.

- 8. Remove the ELC0 condition.

- 9. Wait 5 seconds, then measure output voltage at the PSE.

# 7.1.1.3 Report

- 1. The measured output voltage in step 2.

- The measured output voltage in step 6.

The measured peak output voltage during step 6.

Report whether PSE provided indication of detected ELC0 condition [yes/no].

- 5. The measured output voltage in step 9.

# 7.1.1.4 Expected Results

- 1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

- 2. In step 6, the measured peak voltage on the line SHALL NOT exceed 30V.

- 3. In step 9, the measured output voltage SHALL be in the range of 55.75-60V.

# 7.1.2 ELC1-Short tip-to-ring test

**Test requirement:** Mandatory.

# **7.1.2.1 Test Setup**

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-2.

- 2. The ELC insertion circuit SHALL be set to ELC1, see Figure 6-8 and Table 6-5.

- 3. The loop resistor  $R_{loop}$  SHALL be set to 43 $\Omega$  +/-5%, see Table 6-7.

- 4. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 5. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 6. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

#### 7.1.2.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait 5 seconds, then measure output voltage at the PSE.

- 3. Disconnect the PSE from the test setup.

- 4. Create the ELC1 condition.

- 5. Reconnect the PSE to the test setup.

- 6. Wait 5 seconds, then measure output voltage and current at the PSE.

- 7. Record if the device indicated an ELC1 failure condition

- 8. Remove the ELC1 condition.

- 9. Wait 5 seconds, then measure output voltage at the PSE.

# 7.1.2.3 Report

- 1. The measured output voltage in step 2.

- 2. The measured output voltage in step 6.

- 3. Report whether PSE provided indication of detected ELC1 condition [yes/no].

- 4. The measured output voltage in step 9.

## 7.1.2.4 Expected Results

- 1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

- 2. In step 6, the measured output voltage SHALL be less than 1V and the measured output current SHALL be less than 10 mA.

- 3. In step 9, the measured output voltage SHALL be in the range of 55.75-60V.

# 7.1.3 ELC2-Foreign voltage test

Test requirement: Mandatory.

# 7.1.3.1 Test Setup

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-2.

- 2. The ELC insertion circuit SHALL be set to ELC2, see Figure 6-8 and Table 6-5.

- 3. The loop resistor  $R_{loop}$  SHALL be set to  $43\Omega$  +/-5%, see Table 6-7.

- 4. The DPU signature  $R_{V\text{-SIG}}\,\text{SHALL}$  be set to 24.9k $\Omega$  +/-1%.

- 5. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 6. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

#### 7.1.3.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait for 5 seconds, then measure output voltage at the PSE.

- 3. Disconnect the PSE from the test setup.

- 4. Create the ELC2 condition by inserting the voltage of 3Vdc with Plus connected to the Tip and Minus connected to the Ring.

- 5. Reconnect the PSE to the test setup.

- 6. Wait for 5 seconds, then measure output voltage at the PSE.

- 7. Record if the device indicated an ELC2 failure condition.

- 8. Remove the ELC2 condition.

- 9. Wait for 5 seconds, then measure output voltage at the PSE.

- 10. Disconnect the PSE from the test setup.

- 11. Repeat steps 4-9 with the ELC2 voltage of 40Vdc and 60Vdc.

- 12. Reverse the polarity of the ELC2 voltage.

- 13. Repeat steps 5-10.

# 7.1.3.3 Report

- 1. The measured output voltage in step 2.

- 2. The measured output voltage in step 6.

- 3. Report whether PSE provided indication of detected ELC2 condition [yes/no].

- 4. The measured output voltage in step 9.

# 7.1.3.4 Expected Results

- 1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

- 2. In step 6, the measured output voltage SHALL NOT exceed ELC2 voltage.

- 3. In step 9, the measured output voltage SHALL be in the range of 55.75-60V.

# 7.1.4 ELC3-Off-hook phone test

This test covers the off-hook detection during the start-up phase (MDSU detection and classification).

Test requirement: Mandatory.

### **7.1.4.1 Test Setup**

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-4.

- 2. Off-hook emulator circuitry SHALL be connected with toggle switches S1...S6 in an off position (see Figure 6-10).

- 3. The loop resistor  $R_{loop}$  SHALL be set to 43 $\Omega$  +/-5%, see Table 6-7.

- 4. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 5. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 6. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

#### 7.1.4.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait 5 seconds, then measure output voltage at the PSE.

- 3. Disconnect the PSE from the test setup.

- 4. Turn on switch S1.

- 5. Reconnect the PSE to the test setup.

- 6. Wait 1 second, then measure output voltage at the PSE (see Note 1).

7. Turn off switch S1.

8. Wait 5 seconds, then measure output voltage at the PSE.

- 9. Disconnect the PSE from the test setup.

- 10. Turn on switch S4.

- 11. Reconnect the PSE to the test setup.

- 12. Wait 1 second, then measure output voltage at the PSE (see Note 1).

- 13. Turn off switch S4.

- 14. Wait 5 seconds, then measure output voltage at the PSE.

- 15. Disconnect the PSE from the test setup.

- 16. Turn on switch S2.

- 17. Reconnect the PSE to the test setup.

- 18. Wait 1 second, then measure output voltage at the PSE (see Note 1).

- 19. Turn off switch S2.

- 20. Wait 5 seconds, then measure output voltage at the PSE.

- 21. Disconnect the PSE from the test setup.

- 22. Turn on switch S3.

- 23. Reconnect the PSE to the test setup.

- 24. Wait 1 second, then measure output voltage at the PSE (see Note 1).

- 25. Turn off switch S3.

- 26. Wait 5 seconds, then measure output voltage at the PSE.

Note 1: Voltage measurements SHALL NOT be made during the PSE detection or classification phase, where, the PSE may injector voltage onto the line for the purpose of DPU detection or classification.

# 7.1.4.3 Report

- 1. The measured DC output voltage in steps 2, 6, 8, 12, 14, 18, 20, 24, 26.

- 2. Report whether PSE provided indication of detected ELC3 condition [yes/no].

#### 7.1.4.4 Expected Results

- 1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

- 2. In step 6, the measured output voltage SHALL be less than 1V.

- 3. In step 8, the measured output voltage SHALL be in the range of 55.75-60V.

- 4. In step 12, the measured output voltage SHALL be less than 1V.

- 5. In step 14, the measured output voltage SHALL be in the range of 55.75-60V.

- 6. In step 18, the measured output voltage SHALL be less than 1V.

- 7. In step 20, the measured output voltage SHALL be in the range of 55.75-60V.

- 8. In step 24, the measured output voltage SHALL be less than 1V.

- 9. In step 26, the measured output voltage SHALL be in the range of 55.75-60V.

# 7.2 Start-up tests

# 7.2.1 Line detection test during start-up

Purpose of this test is to ensure that a PSE can start up upon detection of the valid DPU signature. Also, to test a PSE ability to detect non-valid DPU signature values. Test requirement: Mandatory.

# 7.2.1.1 Test Setup

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-1.

- 2. The loop resistor  $R_{loop}$  SHALL be set to  $4\Omega$  +/-5%, see Table 6-7.

- 3. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 4. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 5. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

#### 7.2.1.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait 5 seconds, then measure PSE output voltage.

- 3. Disconnect the PSE from the test setup.

- 4. Set DPU signature  $R_{V-SIG}$  to 33.6 K +/-1%.

- 5. Reconnect the PSE to the test setup.

- 6. Wait 5 seconds, then measure PSE output voltage over a 5 second period. Record the peak value during this period.

- 7. Disconnect the PSE from the test setup.

- 8. Set DPU signature  $R_{V-SIG}$  to 14.7 K +/-1%.

- 9. Repeat steps 5-7.

- 10. Set the loop resistor  $R_{loop}$  to  $43\Omega$  +/-5%, see Table 6-7.

- 11. Repeat steps 1-9.

# 7.2.1.3 Report

- 1. The measured output voltage in step 2.

- 2. The measured peak output voltage in step 6.

# 7.2.1.4 Expected Results

- 1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

- 2. In step 6, the measured peak output voltage SHALL be less than 10V.

# 7.2.2 Test of PSE RPF power classes and classification signature

**Test requirement:** Mandatory.

## **7.2.2.1 Test Setup**

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-1.

- 2. The loop resistor  $R_{loop}$  SHALL be set to  $4\Omega$  +/-5%, see Table 6-7.

- 3. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 4. The DPU emulator Power Class resistor SHALL be set

- a. (Case 1: PSE and DPU power classes match) to the power class that corresponds to the tested PSE power class, see Table 6-4.

- b. (Case 2: PSE and DPU power classes mismatch) as follows:

- i. For PSE class SR3, set DPU emulator to class SR2 (see Table 6-4)

- ii. For PSE class SR2, set DPU class SR3 (see table 6.4)

- iii. For PSE class SR1, set DPU emulator to SR2 (see Table 6-4)

- c. (Case 3: PSE and DPU power classes mismatch) as follows:

- i. For PSE class SR3, set DPU emulator to class SR1 (see Table 6-4)

- ii. For PSE class SR2, set DPU class SR1 (see Table 6-4)

- iii. For PSE class SR1, set DPU emulator to SR3 (see Table 6-4)

- 5. The electronic load ( $I_{SRi}$ ) SHALL be set to 10mA, see 6.1.1.3.

## 7.2.2.2 Method of Procedure

- 1. Set the DPU emulator power class resistor according to Case 1 settings.

- 2. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 3. Wait 5 seconds, then measure output voltage at the PSE.

- 4. Disconnect the PSE from the test setup.

- 5. Repeat steps 2-4 for Case 2 and Case 3 power class settings.

# 7.2.2.3 Report

1. The measured output voltage in step 3.

# 7.2.2.4 Expected Results

- 1. In step 3,

- a. For Case 1: DC output voltage SHALL in the range 55.75-60V, which indicates that PSE and DPU power classes match.

- b. For Case 2: PSE voltage pulses SHALL be less than 20.5V on U-R interface, which indicates that PSE and DPU power classes do not match.

- c. For Case 3: PSE voltage pulses SHALL be less than 20.5V on U-R interface, which indicates that PSE and DPU power classes do not match.

# 7.2.3 Start-up in presence of MELT signature

Test requirement: Mandatory.

# **7.2.3.1 Test Setup**

- 1. The PSE and DPU emulator SHALL be connected to the test setup shown in Figure 6-3.

- 2. The loop resistor  $R_{loop}$  SHALL be set to  $43\Omega + 1/-5\%$ , see Table 6-7.

- 3. The DPU signature  $R_{V-SIG}$  SHALL be set to 24.9k $\Omega$  +/-1%.

- 4. The RPF Power Class resistor SHALL be set to the power class that corresponds to the tested PSE power class, see Table 6-4.

- 5. The electronic load (I<sub>SRi</sub>) SHALL be set to 10mA, see 6.1.1.3.

- 6. The MELT signature SHALL be set to DR type, see Table 6-8.

#### 7.2.3.2 Method of Procedure

- 1. Apply input power to the PSE, wait until the PSE is fully operational, and connect the PSE to the test setup.

- 2. Wait 5 seconds, then measure output voltage at the PSE.

- 3. Disconnect the PSE from the test setup.

- 4. Repeat steps 1-3 with the MELT signature set to ZRC type and RC type.

#### 7.2.3.3 Report

1. The measured output voltage in step 2.

# 7.2.3.4 Expected Results

1. In step 2, the measured output voltage SHALL be in the range of 55.75-60V.

#### 7.3 Normal operation tests

The purpose of this test is to verify that the output voltage, continuous output current and continuous output power of a PSE in a normal operation state (i.e., steady state when PSE reversely powers a DPU) comply with Table 7-1. Electrical parameters in Table 7-1 are originally defined in Table 35 in [3].

PSE electrical specification applies to U-R interface when a power splitter is integrated in a PSE. When an external power splitter is used as a standalone device, Table 7-1 applies to U-R2P interface.

Table 7-1 - PSE electrical specification on U-R interface

| Parameter                                         | Symbol              | Unit | Min       | Max                                             | Comments                                                                                                                                                                       |