## TR-286 Testing of Metallic Line Testing (MELT) functionality on xDSL Ports

Issue: 1 Issue Date: November 2012

#### Notice

The Broadband Forum is a non-profit corporation organized to create guidelines for broadband network system development and deployment. This Broadband Forum Technical Report has been approved by members of the Forum. This Broadband Forum Technical Report is not binding on the Broadband Forum, any of its members, or any developer or service provider. This Broadband Forum Technical Report is subject to change, but only with approval of members of the Forum. This Technical Report is copyrighted by the Broadband Forum, and all rights are reserved. Portions of this Technical Report may be copyrighted by Broadband Forum members.

This Broadband Forum Technical Report is provided AS IS, WITH ALL FAULTS. ANY PERSON HOLDING A COPYRIGHT IN THIS BROADBAND FORUM TECHNICAL REPORT, OR ANY PORTION THEREOF, DISCLAIMS TO THE FULLEST EXTENT PERMITTED BY LAW ANY REPRESENTATION OR WARRANTY, EXPRESS OR IMPLIED, INCLUDING, BUT NOT LIMITED TO, ANY WARRANTY:

- (A) OF ACCURACY, COMPLETENESS, MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, NON-INFRINGEMENT, OR TITLE;

- (B) THAT THE CONTENTS OF THIS BROADBAND FORUM TECHNICAL REPORT ARE SUITABLE FOR ANY PURPOSE, EVEN IF THAT PURPOSE IS KNOWN TO THE COPYRIGHT HOLDER;

- (C) THAT THE IMPLEMENTATION OF THE CONTENTS OF THE TECHNICAL REPORT WILL NOT INFRINGE ANY THIRD PARTY PATENTS, COPYRIGHTS, TRADEMARKS OR OTHER RIGHTS.

By using this Broadband Forum Technical Report, users acknowledge that implementation may require licenses to patents. The Broadband Forum encourages but does not require its members to identify such patents. For a list of declarations made by Broadband Forum member companies, please see <a href="http://www.broadband-forum.org">http://www.broadband-forum.org</a>. No assurance is given that licenses to patents necessary to implement this Technical Report will be available for license at all or on reasonable and non-discriminatory terms.

ANY PERSON HOLDING A COPYRIGHT IN THIS BROADBAND FORUM TECHNICAL REPORT, OR ANY PORTION THEREOF, DISCLAIMS TO THE FULLEST EXTENT PERMITTED BY LAW (A) ANY LIABILITY (INCLUDING DIRECT, INDIRECT, SPECIAL, OR CONSEQUENTIAL DAMAGES UNDER ANY LEGAL THEORY) ARISING FROM OR RELATED TO THE USE OF OR RELIANCE UPON THIS TECHNICAL REPORT; AND (B) ANY OBLIGATION TO UPDATE OR CORRECT THIS TECHNICAL REPORT.

Broadband Forum Technical Reports may be copied, downloaded, stored on a server or otherwise re-distributed in their entirety only, and may not be modified without the advance written permission of the Broadband Forum.

The text of this notice must be included in all copies of this Broadband Forum Technical Report.

### **Issue History**

| Issue Number | <b>Approval Date</b> | <b>Publication Date</b> | <b>Issue Editor</b> | Changes  |

|--------------|----------------------|-------------------------|---------------------|----------|

| 1            | 26 November          | 17 December             | Aleksandra          | Original |

|              | 2012                 | 2012                    | Kozarev,            |          |

|              |                      |                         | Lantiq              |          |

Comments or questions about this Broadband Forum Technical Report should be directed to info@broadband-forum.org.

| Editor                                       | Aleksandra Kozarev                | Lantiq              |

|----------------------------------------------|-----------------------------------|---------------------|

| Metallic Transmission<br>Working Group Chair | Les Brown                         | Lantiq              |

| Vice Chairs                                  | Massimo Sorbara<br>Lincoln Lavoie | Ikanos<br>UNH       |

| Chief Editor                                 | Michael Hanrahan                  | Huawei Technologies |

## **Table of Contents**

| E | XECUTIV        | 'E SUMMARY                                                                                               | 9  |

|---|----------------|----------------------------------------------------------------------------------------------------------|----|

| 1 | PURF           | OSE AND SCOPE                                                                                            | 10 |

|   | 1.1 PU         | RPOSE                                                                                                    |    |

|   |                | )PE                                                                                                      |    |

| 2 | DEFE           | RENCES AND TERMINOLOGY                                                                                   | 11 |

| 4 |                |                                                                                                          |    |

|   |                | NVENTIONS                                                                                                |    |

|   |                | TERENCES                                                                                                 |    |

|   |                | FINITIONS                                                                                                |    |

|   |                |                                                                                                          |    |

| 3 | TECH           | INICAL REPORT IMPACT                                                                                     | 14 |

|   | 3.1 EN         | ERGY EFFICIENCY                                                                                          | 14 |

|   | 3.2 IPv        | 6                                                                                                        | 14 |

|   |                | URITY                                                                                                    |    |

|   | 3.4 Pri        | VACY                                                                                                     | 14 |

| 4 | GENI           | RAL TESTING REQUIREMENTS                                                                                 |    |

| - |                | stem Under Test (SUT) Settings                                                                           |    |

|   |                | TEM UNDER TEST (SUT) SETTINGS                                                                            |    |

|   |                | T SETUP                                                                                                  |    |

|   |                | LT SPECIFIC TEST CIRCUITS                                                                                |    |

|   | 4.4.1          | Test Resistor                                                                                            |    |

|   | 4.4.2          | Test Capacitor                                                                                           |    |

|   | 4.4.3          | Foreign Voltage Source                                                                                   |    |

|   | 4.4.4          | Far-end Signature                                                                                        |    |

|   | 4.4.5          | Line Model for the Far-end Signature Identification                                                      |    |

|   |                | LT-PMD CONFIGURATION PARAMETERS                                                                          |    |

|   | 4.5.1          | Measurement Class (MELT-MCLASS)                                                                          |    |

|   | 4.5.2<br>4.5.3 | Peak Metallic Voltage between Tip and Ring (MELT-PV)<br>Signal Frequency for active AC Tests (MELT-AC-F) |    |

|   | 4.5.4          | Pair Identification Tone Frequency (MELT-PIT-F)                                                          |    |

|   | 4.5.5          | Maximum Far-end Signature Conduction Voltage (MELT-MAXFE-SCV)                                            |    |

|   | 4.5.6          | Minimum Far-end Signature Conduction Voltage (MELT-MINFE-SCV)                                            |    |

|   | 4.6 ME         | LT-P CONFIGURATION PARAMETERS                                                                            |    |

|   | 4.6.1          | Loop resistance classification threshold (MELT-LRC-TH)                                                   |    |

|   | 4.6.2          | Loop parameters per unit length (MELT-LOOP-PARAMS)                                                       |    |

|   | 4.6.3          | Hazardous DC voltage level (MELT-HDCV-L)                                                                 |    |

|   | 4.6.4          | Hazardous AC voltage level (MELT-HACV-L)                                                                 |    |

|   | 4.6.5          | Foreign EMF DC voltage level (MELT-FDCV-L)                                                               |    |

|   | 4.6.6<br>4.6.7 | Foreign EMF AC voltage level (MELT-FACV-L)<br>System capacitance at the CPE side (MELT-SYSC-CPE)         |    |

| 5 |                | 5-PMD TESTING                                                                                            |    |

| 5 |                |                                                                                                          |    |

|   |                | LT-PMD TEST CASES FOR MEASUREMENT FUNCTIONS<br>The 4-Element DC Resistance                               |    |

|   | 5.1.1<br>5.1.2 | The 4-Element DC Resistance                                                                              |    |

|   | 5.1.2          | Measurement of foreign voltages                                                                          |    |

|   | 5.1.3          | Loop Capacitance                                                                                         |    |

|   | 5.1.5          | Loop Resistance                                                                                          |    |

|   | 5.1.6          | The 3-Element complex admittance                                                                         |    |

|   | 5.1.7          | Loop complex admittance                                                                                  |    |

|   |                | LT-PMD Test Cases for Non-Measurement Functions                                                          |    |

|   | 5.2.1          | Pair identification tone measurement                                                                     |    |

|   |                | LT-PMD TEST CASES FOR REPORTING PARAMETERS                                                               |    |

|   | 5.3.1          | Measurement frequency for active AC tests                                                                |    |

|   | 5.3.2 Input impedance for foreign voltage measurements |    |

|---|--------------------------------------------------------|----|

| 6 | 5 MELT-P TESTING                                       |    |

|   | 6.1 IDENTIFICATION OF AN OPEN WIRE FAILURE             | 40 |

|   | 6.2 IDENTIFICATION OF A SHORT CIRCUIT FAILURE          |    |

|   | 6.3 RESISTIVE FAULT IDENTIFICATION                     | 43 |

|   | 6.4 LEAKAGE IDENTIFICATION                             |    |

|   | 6.5 FOREIGN VOLTAGE CLASSIFICATION                     |    |

|   | 6.5.1 Foreign voltage type                             |    |

|   | 6.5.2 Foreign voltage level class                      | 47 |

|   | 6.6 FAR-END SIGNATURE TOPOLOGY IDENTIFICATION          |    |

| 7 | SAME PAIR DSL AND MELT OPERATION                       | 50 |

|   | 7.1 SAME PAIR ADSL2PLUS - MELT TEST                    |    |

|   | 7.2 SAME PAIR VDSL2 - MELT TEST                        | 51 |

|   | 7.3 SAME PAIR SHDSL - MELT TEST                        | 53 |

## List of Tables

| Table 1: Specific Test Profiles                                                            |      |

|--------------------------------------------------------------------------------------------|------|

| Table 2: Test Resistors Values                                                             | . 17 |

| Table 3: Test Capacitors Values                                                            | . 18 |

| Table 4: Foreign Voltages DC Source Values                                                 | . 19 |

| Table 5: Foreign Voltages AC Source Values                                                 | .20  |

| Table 6: Components of the Far-end Signature type DR                                       | .20  |

| Table 7: Components of the Far-end signature type ZRC                                      |      |

| Table 8: Components of the line model 1                                                    |      |

| Table 9: Components of the line model 2                                                    |      |

| Table 10: MELT-MCLASS setting                                                              |      |

| Table 11: MELT-PV setting                                                                  |      |

| Table 12: MELT-AC-F setting                                                                |      |

| Table 12: MELT-PIT-F setting                                                               |      |

| Table 14: MELT-MAXFE-SCV setting                                                           |      |

| Table 14. MELT-MAATE-SCV setting       Table 15: MELT-MINFE-SCV setting                    |      |

| ÷                                                                                          |      |

| Table 16: MELT-LRC-TH setting                                                              |      |

| Table 17: MELT-LOOP-PARAMS setting         Table 19: MELT HDOV L setting                   |      |

| Table 18: MELT-HDCV-L setting         Table 10: MELT-HDCV-L setting                        |      |

| Table 19: MELT-HACV-L setting         Table 20: MELT-FROM L setting                        |      |

| Table 20: MELT-FDCV-L setting                                                              |      |

| Table 21: MELT-FACV-L setting                                                              |      |

| Table 22: MELT- SYSC-CPE setting                                                           |      |

| Table 23: 4-element DC resistance measurement                                              |      |

| Table 24: Test voltages in the 4-element DC resistance measurement                         |      |

| Table 25: Test currents in the 4-element DC resistance measurement                         | . 29 |

| Table 26: 3-element capacitance measurement                                                |      |

| Table 27: Test voltages in the 3-element capacitance measurement                           | . 30 |

| Table 28: Foreign DC voltage measurement                                                   | . 31 |

| Table 29: Foreign AC voltage and frequency measurement                                     | . 32 |

| Table 30: Loop capacitance measurement                                                     | .33  |

| Table 31: Test voltages in the loop capacitance measurement                                |      |

| Table 32: Loop resistance measurement                                                      |      |

| Table 33: Test voltages in the loop resistance measurement                                 |      |

| Table 34: 3-element complex admittance measurement                                         |      |

| Table 35: Test voltages in the 3-element complex capacitance measurement                   |      |

| Table 36: Loop complex admittance measurement                                              |      |

| Table 37: Test voltages in the loop complex admittance measurement                         |      |

| Table 38: Pair identification tone measurement                                             |      |

| Table 39: Maximum absolute difference of a cable capacitance $C_{TG}$ and $C_{RG}$         |      |

| Table 40: Open wire failure test                                                           |      |

| Table 40: Open whe failure test         Table 41: MELT-TRSHORT-TH setting.                 |      |

|                                                                                            |      |

| Table 42: Short circuit failure test         Table 43: Resistive fault identification test | .42  |

|                                                                                            |      |

| Table 44: Leakage identification test                                                      |      |

| Table 45: Foreign voltage type test.                                                       |      |

| Table 46: Foreign voltage level test                                                       |      |

| Table 47: Far-end signature topology identification test                                   |      |

| Table 48: Same Pair MELT – ADSL2plus test.                                                 |      |

| Table 49: Same Pair MELT – VDSL2 test                                                      |      |

| Table 50: Same Pair MELT – SHDSL test                                                      |      |

| Table 51: CTN_1 Components and accuracy limits                                             |      |

| Table 52: CTN_2 Components and accuracy limits                                             |      |

| Table 53: CTN_3 Components and accuracy limits                                             | .56  |

| Table 54: CTN_4 Components and accuracy limits            | 56 |

|-----------------------------------------------------------|----|

| Table 55: MELT measurement for the combined test networks |    |

## List of Figures

| Figure 1: Test setup for MELT testing                                | .16  |

|----------------------------------------------------------------------|------|

| Figure 2: Test setup for Far-end Signature identification            | .16  |

| Figure 3: Test setup for testing DSL system in combination with MELT | .17  |

| Figure 4: Test Resistor                                              | .17  |

| Figure 5: Test Capacitor                                             | .18  |

| Figure 6: Foreign Voltage DC Source                                  | . 19 |

| Figure 7: Foreign Voltage AC source                                  | .19  |

| Figure 8: Far-end Signature type DR                                  | .20  |

| Figure 9: Far-end Signature type ZRC                                 | .21  |

| Figure 10: Line Model for the Far-end Signature Identification       | .21  |

| Figure 11: Composed test network (CTN)                               | .55  |

### **Executive Summary**

TR-286 describes test cases required for verification of the Metallic Line Testing entity (MELT) according to Recommendation ITU-T G.996.2 and collocated with the DSLAM (Digital Subscriber Line Access Multiplexer). In addition, TR-286 provides testing methodology for xDSL systems, such as ITU-T G.992.5 (ADSL2plus), G.993.2 (VDSL2) and G.991.2 (SHDSL), in combination with MELT functionality.

## 1 Purpose and Scope

#### 1.1 Purpose

TR-286 specifies a set of tests to be performed to assure the functionality of the MELT functions (test parameters) and accuracy as defined in Recommendation ITU-T G.996.2 Annex E (MELT-PMD) and Annex F (MELT-P).

#### 1.2 Scope

TR-286 describes test cases required for verification of the Metallic Line Testing entity (MELT) according to Recommendation ITU-T G.996.2, Annex E (MELT-PMD) and F (MELT-P) that is collocated with the DSLAM (Digital Subscriber Line Access Multiplexer). Additionally, it focuses on xDSL data transmission tests and stability criteria in combination with MELT functions. xDSL operation is specified by ITU-T Recommendations G.992.3 (ADSL2), G.992.5 (ADSL2plus), G.993.2 (VDSL2), and G.991.2 (SHDSL).

The equipment under test includes network-end equipment (such as a DSLAM), Metallic Line testing entity (MELT), MELT specific test circuits (MTC) and customer-end equipment (such as a CPE). It is assumed that the individual DSL transceivers (DSLAM and CPE) also pass applicable DSL-specific testing requirements specified in TR-100 and TR-105 (ADSL2/ADSL2plus), TR-114 and TR-115 (VDSL2), and TR-60 (SHDSL).

## 2 References and Terminology

#### 2.1 Conventions

In this Technical Report, several words are used to signify the requirements of the specification. These words are always capitalized. More information can be found be in RFC 2119 [10].

| SHALL      | This word, or the term "REQUIRED", means that the definition is an absolute requirement of the specification.                                                                                                                                                                                                                         |

|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SHALL NOT  | This phrase means that the definition is an absolute prohibition of the specification.                                                                                                                                                                                                                                                |

| SHOULD     | This word, or the term "RECOMMENDED", means that there could exist valid reasons in particular circumstances to ignore this item, but the full implications need to be understood and carefully weighed before choosing a different course.                                                                                           |

| SHOULD NOT | This phrase, or the phrase "NOT RECOMMENDED" means that there could<br>exist valid reasons in particular circumstances when the particular behavior<br>is acceptable or even useful, but the full implications need to be understood<br>and the case carefully weighed before implementing any behavior described<br>with this label. |

| MAY        | This word, or the term "OPTIONAL", means that this item is one of an allowed set of alternatives. An implementation that does not include this option SHALL be prepared to inter-operate with another implementation that does include the option.                                                                                    |

#### 2.2 References

The following references are of relevance to this Technical Report. At the time of publication, the editions indicated were valid. All references are subject to revision; users of this Technical Report are therefore encouraged to investigate the possibility of applying the most recent edition of the references listed below.

A list of currently valid Broadband Forum Technical Reports is published at <u>www.broadband-forum.org</u>.

| Doc | ument             | Title                                                                     | Source | Year |

|-----|-------------------|---------------------------------------------------------------------------|--------|------|

| [1] | TR-100<br>Issue 2 | ADSL2/2plus Performance Test Plan                                         | BBF    | 2012 |

| [2] | TR-105<br>Issue 2 | ADSL2/2plus Functionality Test Plan                                       | BBF    | 2012 |

| [3] | TR-114            | VDSL2 Performance Test Plan, including all in force errata and amendments | BBF    | 2009 |

| [4] | TR-115            | VDSL2 Functionality Test Plan                                             | BBF    | 2012 |

Issue 2

| [5]  | G.996.2  | Single-ended line testing for digital subscriber lines (DSL), including all in force errata and amendments                                        | ITU-T | 2009 |

|------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|

| [6]  | G.992.5  | Asymmetric Digital Subscriber Line (ADSL) transceivers<br>- Extended bandwidth ADSL2 (ADSL2plus), including<br>all in force errata and amendments | ITU-T | 2009 |

| [7]  | G.993.2  | Very high speed subscriber line transceivers 2 (VDSL2),<br>including all in force errata and amendments                                           | ITU-T | 2011 |

| [8]  | G.991.2  | Single-pair high speed digital subscriber line (SHDSL)<br>transceivers, including all in force errata and<br>amendments                           | ITU-T | 2003 |

| [9]  | G.997.1  | Physical Layer Management for Digital Subscriber Line<br>(DSL) Transceivers, including all in force errata and<br>amendments                      | ITU-T | 2009 |

| [10] | RFC 2119 | <i>Key words for use in RFCs to Indicate Requirement Levels</i>                                                                                   | IETF  | 1997 |

|      |          |                                                                                                                                                   |       |      |

#### 2.3 Definitions

The following terminology is used throughout this Technical Report.

| GND            | Ground                                                                                                                                                                                                                  |  |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ID tone        | Pair identification tone                                                                                                                                                                                                |  |

| IDLE state     | <ul><li>a) MELT entity is inactive but ready to start the PMD measurements</li><li>b) DSL port powered but no data transmitted</li></ul>                                                                                |  |

| RING           | RING wire (in some countries also known as a-wire, B-wire) is negative<br>with respect to the TIP wire when the pair-identification tone is turned on.<br>This definition MUST be used consistently for all MELT tests. |  |

| Showtime state | e DSLAM and CPE trained up to the point of passing data                                                                                                                                                                 |  |

| Sync state     | Showtime state                                                                                                                                                                                                          |  |

| TIP            | TIP wire (in some countries also known as b-wire, A-wire) is positive with<br>respect to the RING wire when the pair-identification tone is turned on.<br>This definition MUST be used consistently for all MELT tests  |  |

#### 2.4 Abbreviations

This Technical Report uses the following abbreviations:

| ATU           | ADSL2/2plus Transceiver Unit |

|---------------|------------------------------|

| ATU-C         | ATU at the DSLAM             |

| ATU-R         | ATU at the CPE               |

| CTN           | Composed MELT Test Network   |

| CV (-C, -CFE) | Code Violation               |

| ES (-L, -LFE) | Error Second                 |

| FS            | Far-end Signature            |

| FVAC          | Foreign Voltage AC Source    |

| FVDC           | Foreign Voltage DC Source                |  |  |

|----------------|------------------------------------------|--|--|

| MELT           | Metallic line testing entity             |  |  |

| MELT-P         | MELT - Processing                        |  |  |

| MELT-PMD       | MELT - Physical Medium Dependent         |  |  |

| MTC            | MELT specific Test Circuitry             |  |  |

| SES (-L, -LFE) | Severely Errored Second                  |  |  |

| STU            | SHDSL Transceiver Unit                   |  |  |

| STU-C          | STU at the DSLAM                         |  |  |

| STU-R          | STU at the CPE                           |  |  |

| TCPAM          | Trellis Coded Pulse Amplitude Modulation |  |  |

| VTU            | VDSL2 Transceiver Unit                   |  |  |

| VTU-O          | VTU at the DSLAM                         |  |  |

| VTU-R          | VTU at the CPE                           |  |  |

## **3** Technical Report Impact

### 3.1 Energy Efficiency

TR-286 has no impact on energy efficiency.

#### 3.2 IPv6

TR-286 has no impact on IPv6.

#### 3.3 Security

TR-286 has no impact on security.

### 3.4 Privacy

TR-286 has no impact on privacy.

## 4 General Testing Requirements

#### 4.1 System Under Test (SUT) Settings

For MELT testing the following settings are applicable to VDSL2 [7], ADSL2plus [6] and SHDSL [8] ports.

For VDSL2 ports, the following settings SHALL be used:

- VDSL2 band defined in Table 1/TR-115 [4]

- Common line settings defined in Section 4.2.2.1/TR-115

- Specific line setting RA\_I\_150\_150 defined in Table 11/TR-115

For ADSL2plus ports, the following settings SHALL be used:

- Common line settings defined in Table 4-1/TR-105 [2]

- Specific test profiles A2P\_RA\_I\_30000k, B2P\_RA\_I\_30000k or J2P60\_RA\_I\_30000k defined in Table 1, depending on the operation mode of the system under test

- General line settings I-16/2 defined in Table 4.3 in TR-105

| Specific<br>Test<br>Profile | General<br>line setting<br>DS | General<br>line setting<br>US | XTSE                            | RA-Mode | DS net data<br>rate (kbit/s)<br>(max-min) | US net data<br>rate (kbit/s)<br>(max-min) |

|-----------------------------|-------------------------------|-------------------------------|---------------------------------|---------|-------------------------------------------|-------------------------------------------|

| A2P_RA_I<br>_30000k         | I-16/2                        | I-16/2                        | G.992.5<br>Annex A              | AT_INIT | 30000-32                                  | 2016-32                                   |

| B2P_RA_I<br>_30000k         | I-16/2                        | I-16/2                        | G.992.5<br>Annex B              | AT_INIT | 30000-32                                  | 2016-32                                   |

| J2P60_RA<br>_I_30000k       | I-16/2                        | I-16/2                        | G.992.5<br>Annex J<br>(ADLU-60) | AT_INIT | 30000-32                                  | 4032-32                                   |

#### Table 1: Specific Test Profiles

For SHDSL ports, the following profiles SHALL be used:

#### 1.TCPAM-16

- Symmetric PSD as defined in G.991.2 [8]

- 16-TCPAM modulation

- Fixed data rate set to 384kbs, 512kbps, 1024kbps and 2048kbps

- Line probe (PMMS) disabled

#### 2. TCPAM-32

- Symmetric PSD as defined in G.991.2

- 32-TCPAM modulation

- Fixed data rate set to 2560kbps, 4096kbps and 5696kbs

- Line probe (PMMS) disabled

No special SUT configuration for MELT testing is needed unless otherwise stated in the related test case. MELT functionality MUST be available with the initial setup. The xDSL configuration SHALL NOT have impact on the MELT functionality.

#### 4.2 Test Plan Passing Criteria

For each test case, the actual values of components in the applicable MELT specific test circuitry (MTC) SHALL be determined by a measuring device (e.g. multimeter), prior to performing any MELT test. The maximum deviation of each component of the MTC from its nominal value SHALL meet the required tolerance limits defined in Section 4.4. Also, the measuring device SHALL meet the required accuracy limits as defined in Section 4.4.

The pass/fail criterion is defined on a per test case basis and it SHALL take into consideration the following three elements: the actual value of the MTC, the accuracy of the measuring device and the accuracy of the MELT entity.

#### 4.3 Test Setup

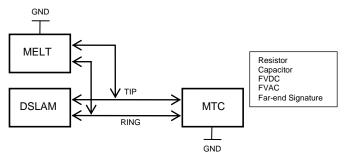

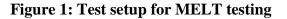

A typical test setup for MELT testing consists of three elements shown in Figure 1: DSLAM, Metallic Line Testing entity (MELT) and MELT specific test circuits (MTC). The MTC (Resistor, Capacitor, DC foreign voltage source (FVDC) and AC foreign voltage source (FVAC)) is connected either between TIP and RING, TIP and Ground (GND) or RING and GND. Test setup for the far-end signature identification is shown in Figure 2. The Far-end signatures (FS) SHALL be connected only between TIP and RING.

Figure 2: Test setup for Far-end Signature identification

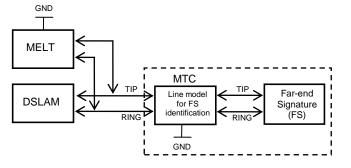

Test setup for testing xDSL systems, such as ADSL2plus, VDSL2 and SHDSL, in combination with MELT functionality is shown in Figure 3. It contains the MELT entity and MTC, and a typical test configuration for testing DSL systems, defined for example in TR-105 [2] or TR-115 [4].

Figure 3 shows a typical test setup for testing MELT impact on the same pair SHDSL, ADSL2/2plus and VDSL2 system.

Figure 3: Test setup for testing DSL system in combination with MELT

NOTE: MTC is connected as defined in Figure 1.

#### 4.4 MELT specific test circuits

This section defines the MELT specific test circuits, including the required tolerances of the single components and the accuracy of the measuring device used to determine their actual values (e.g. a multimeter).

See also Section 4.2 for detailed explanation.

#### 4.4.1 Test Resistor

Test resistor is shown in Figure 4 with the appropriate values listed in Table 2. The resistors used to validate the MELT testing procedures SHALL be of a large enough wattage or a low enough thermal coefficient to prevent a resistance variation greater than 0.1% due to self-heating during the testing execution.

**Figure 4: Test Resistor**

| Table 2. Test Resistors Values |                              |                     |  |  |

|--------------------------------|------------------------------|---------------------|--|--|

| Resistor                       | Nominal value                | Multimeter accuracy |  |  |

| R1                             | $10 \ \Omega \pm 5 \ \%$     | $\pm 1 \Omega$      |  |  |

| R2                             | $120 \ \Omega \pm 5 \ \%$    | ±1%                 |  |  |

| R3                             | $270~\Omega\pm5~\%$          | ±1%                 |  |  |

| R4                             | $600~\Omega\pm5~\%$          | ±1%                 |  |  |

| R5                             | $1 \text{ k}\Omega \pm 5 \%$ | ±1%                 |  |  |

Table 2. Test Resistors Values

| R6  | $47 \text{ k}\Omega \pm 5 \text{ \%}$ | ±1%  |

|-----|---------------------------------------|------|

| R7  | $100 \text{ k}\Omega \pm 5 \%$        | ±1%  |

| R8  | $470 \; k\Omega \pm 5 \; \%$          | ±1%  |

| R9  | $1 \text{ M}\Omega \pm 5 \%$          | ±1%  |

| R10 | 4,7 M $\Omega \pm 5$ %                | ±1 % |

| R11 | $6,8~M\Omega\pm5~\%$                  | ±1%  |

| R12 | $10 \text{ M}\Omega \pm 5 \%$         | ±1%  |

| R13 | OPEN                                  |      |

#### 4.4.2 Test Capacitor

Test capacitor is shown in Figure 5 with the appropriate values listed in Table 3. The capacitors used to validate the MELT testing procedures SHALL be of a type for which the apparent capacitance does not change as a function of the AC or DC voltage applied to them. Otherwise, correlation between the MELT results and the multimeter results may not be possible due to the use of different testing voltages.

**Figure 5: Test Capacitor**

| Capacitor | Nominal value             | Multimeter accuracy |

|-----------|---------------------------|---------------------|

| C1        | OPEN                      |                     |

| C2        | 10 nF ± 5 %               | ± 1nF               |

| C3        | $22 nF \pm 5 \%$          | $\pm 1 nF$          |

| C4        | $47~nF\pm5~\%$            | $\pm 1 nF$          |

| C5        | $100 \text{ nF} \pm 5 \%$ | ± 1%                |

| C6        | $470 \text{ nF} \pm 5 \%$ | ± 1%                |

| C7        | $1~\mu F \pm 5~\%$        | ± 1%                |

| C8        | $4,7\mu F\pm5~\%$         | ± 1%                |

**Table 3: Test Capacitors Values**

#### 4.4.3 Foreign Voltage Source

Foreign voltage DC source is shown in Figure 6 with the appropriate values listed in Table 4. The voltage source used to validate the MELT testing procedures SHALL be able to sink or source any current that may appear during the testing execution while maintaining a constant output voltage, except for the normal voltage drop across its source resistance.

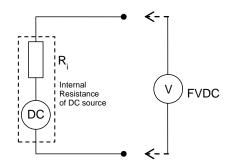

Figure 6: Foreign Voltage DC Source

| FVDC   | Nominal value | Multimeter accuracy |

|--------|---------------|---------------------|

| FVDC1  | OPEN          |                     |

| FVDC2  | 20 V          | $\pm 0.5 \text{ V}$ |

| FVDC3  | 115 V         | ±1%                 |

| FVDC4  | 125 V         | ±1%                 |

| FVDC5  | 180 V         | ±1%                 |

| FVDC6  | 250 V         | ±1%                 |

| FVDC7  | - 20 V        | $\pm 0.5 \text{ V}$ |

| FVDC8  | - 48 V        | ±1%                 |

| FVDC9  | - 96 V        | ±1%                 |

| FVDC10 | - 115 V       | ±1%                 |

| FVDC11 | - 125 V       | ±1%                 |

| FVDC12 | - 180 V       | ±1%                 |

| FVDC13 | - 250 V       | ±1%                 |

**Table 4: Foreign Voltages DC Source Values**

Each nominal value of the DC voltage (FVDC) SHALL be verified by means of a measuring device (V) and if necessary adjusted at the output of the DC voltage source, before performing any MELT Voltage test.

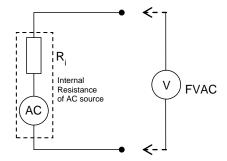

Foreign voltage AC source is shown in Figure 7 with the appropriate values listed in Table 5.

Figure 7: Foreign Voltage AC source

| FVAC                                                                                                                        | Nominal value | Multimeter accuracy |

|-----------------------------------------------------------------------------------------------------------------------------|---------------|---------------------|

| FVAC1                                                                                                                       | OPEN          |                     |

| FVAC2                                                                                                                       | 20 Vrms       | $\pm 0.5$ Vrms      |

| FVAC3                                                                                                                       | 47 Vrms       | $\pm 0.5$ Vrms      |

| FVAC4                                                                                                                       | 53 Vrms       | ±1%                 |

| FVAC5                                                                                                                       | 160 Vrms      | ± 1 %               |

| FVAC6                                                                                                                       | 250 Vrms      | ±1%                 |

| NOTE: frequency of the foreign voltage AC source is $16 2/3$ , $25$ , $50$ or $60$ Hz. Multimeter accuracy is $\pm 0.1$ Hz. |               |                     |

| Table 5: Foreign | Voltages | <b>AC Source Values</b> |

|------------------|----------|-------------------------|

| rubic of rongin  | 1 onuges | no bource values        |

Each nominal value of the AC voltage (FVAC) SHALL be verified by means of a measuring device (V) and if necessary adjusted at the output of the AC voltage source, before performing any MELT Voltage test.

#### 4.4.4 Far-end Signature

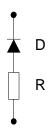

Two types of the Far-end signature (FS) are shown in Figure 8 and Figure 9, with appropriate components listed in Table 6 and Table 7.

Figure 8: Far-end Signature type DR

|            | Nominal value                          | Multimeter accuracy |

|------------|----------------------------------------|---------------------|

| R          | $470 \text{ k}\Omega \pm 1 \text{ \%}$ | n.a. / see NOTE     |

| $U_{f}(D)$ | 0,7 V(at $I_f$ = 10 mA) $\pm$ 0.1 V    | n.a. / see NOTE     |

Table 6: Components of the Far-end Signature type DR

In the ZRC signature type, the 6.8 V zener diodes are used to make the signature appear high impedance for low voltage signals. They need to have a high impedance in comparison to the 100 k $\Omega$  and 470 nF components. Assuming the signal frequency is high enough for the capacitor to be much lower than 100 k $\Omega$ , the zener diode needs to be high impedance in comparison to 100 k $\Omega$ . Using an arbitrary factor of 10 gives a 1 M $\Omega$  impedance at 6 V and implies a reverse leakage current of less than 6  $\mu$ A at 6 V. On the other hand, the 100 k $\Omega$  resistor seriously limits the current that can be pushed through the zener diode in its conduction region. Therefore the 6.8 V zener knee voltage must be defined at a very low current level. Some zener diodes are available that have their knee defined at 50  $\mu$ A and consequently they have a low reverse conduction current. They would be suitable for this application.

#### Figure 9: Far-end Signature type ZRC

|                     | Nominal value                         | Multimeter accuracy |

|---------------------|---------------------------------------|---------------------|

| R                   | $100 \text{ k}\Omega \pm 1 \%$        | n.a. / see NOTE     |

| С                   | $470 \text{ nF} \pm 1 \text{ \%}$     | n.a. / see NOTE     |

| U <sub>z</sub> (D1) | $6.8~V\pm5$ % @ 50 $\mu A$            | n.a. / see NOTE     |

| U <sub>z</sub> (D2) | $6.8 \ V \pm 5 \ \% \ @ \ 50 \ \mu A$ | n.a. / see NOTE     |

Table 7: Components of the Far-end signature type ZRC

NOTE: In case of using far-end signatures as an MTC, it is not needed to determine the actual values of the components by means of a measuring device. The purpose of the test is to verify if the MELT can detect the far-end signature. It is not required for the MELT to measure the single components of any far-end signature.

#### 4.4.5 Line Model for the Far-end Signature Identification

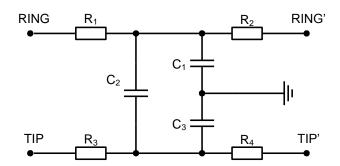

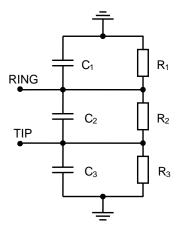

Line model for the Far-end signature (FS) identification is shown in Figure 10. Two settings of the line model components, representing a 4.5km long 0.4mm twisted pair and a 10.5km long 0.6mm cable, are defined in Table 8 and Table 9.

The resistors used to implement the line model SHALL be of a large enough wattage or a low enough thermal coefficient to prevent a resistance variation greater than 0.1% due to self-heating during the testing execution. The capacitors used to implement the line model SHALL be of a type for which the apparent capacitance doesn't change as a function of the AC or DC voltage applied to them.

Figure 10: Line Model for the Far-end Signature Identification

|    | Nominal value                     | Multimeter accuracy |

|----|-----------------------------------|---------------------|

| R1 | $300~\Omega\pm5~\%$               | ±1%                 |

| R2 | $300~\Omega\pm5~\%$               | ±1%                 |

| R3 | $300~\Omega\pm5~\%$               | ±1%                 |

| R4 | $300~\Omega\pm5~\%$               | ± 1%                |

| C1 | $300 \text{ nF} \pm 5 \text{ \%}$ | ±1%                 |

| C2 | $55 \text{ nF} \pm 5 \%$          | ±1%                 |

| C3 | $300 \text{ nF} \pm 5 \text{ \%}$ | ±1%                 |

Table 8: Components of the line model 1

#### Table 9: Components of the line model 2

|    | Nominal value             | Multimeter accuracy |

|----|---------------------------|---------------------|

| R1 | $300 \ \Omega \pm 5 \ \%$ | ± 1%                |

| R2 | $300 \ \Omega \pm 5 \ \%$ | ± 1%                |

| R3 | $300~\Omega\pm5~\%$       | ± 1%                |

| R4 | $300 \ \Omega \pm 5 \ \%$ | ± 1%                |

| C1 | $600 \text{ nF} \pm 5 \%$ | ± 1%                |

| C2 | $100 \text{ nF} \pm 5 \%$ | ± 1%                |

| C3 | $600~nF\pm5~\%$           | ± 1%                |

#### 4.5 MELT-PMD Configuration Parameters

This section describes the configuration parameters of the MELT-PMD function. When validating the system under test, the configurable parameters should be set to the values listed as "Configuration settings" in the following tables. Note that in some cases, the system MAY autonomously use the closest available value if the listed value is not supported.

#### 4.5.1 Measurement Class (MELT-MCLASS)

Parameter MELT-MCLASS defines the list of measurements to be executed:

- The same combined measurement of the 4-element DC resistance, 3-element capacitance and foreign DC and AC voltage SHALL apply in a consecutive manner to the following test cases: 4-element DC resistance measurement (test case 5.1.1), 3-element capacitance measurement (test case 5.1.2) and foreign DC and AC voltage measurements (test case 5.1.3)

- A single measurement SHALL apply for the following test cases: loop capacitance (test case 5.1.4), loop resistance (test case 5.1.5), 3-element complex admittance (test case 5.1.6) and loop complex admittance (test case 5.1.7)

MELT-MCLASS setting is defined in Table 10.

| List of<br>measurements                         | Range                                      | Configuration<br>settings                                                                                                                                                                                  |

|-------------------------------------------------|--------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| List of<br>MELT-PMD<br>measurement<br>functions | single measurement or combined measurement | <i>test cases 5.1.4-5.1.7:</i> single measurement<br><i>test cases 5.1.1-5.1.3:</i> same combined<br>measurement of the 4-element DC<br>resistance, 3-element capacitance and<br>foreign DC and AC voltage |

#### Table 10: MELT-MCLASS setting

#### 4.5.2 Peak Metallic Voltage between Tip and Ring (MELT-PV)

Parameter MELT-PV defines the peak metallic voltage which must not be exceeded in any active measurement applying a metallic voltage between tip and ring in order to avoid operation in a non-linear range of termination located at the far-end during the measurement.

MELT-PV setting is defined in Table 11.

#### Table 11: MELT-PV setting

| Peak metallic voltage                      | Range   | Configuration<br>settings |

|--------------------------------------------|---------|---------------------------|

| Peak metallic voltage between tip and ring | 0 100 V | 45 V                      |

#### 4.5.3 Signal Frequency for active AC Tests (MELT-AC-F)

Parameter MELT-AC-F defines the frequency used during the 3-element capacitance test, if performed using a sine wave signal, and during the 3-element complex admittance test. The supported set of frequencies is at the vendor's discretion with an option to operate in automatic mode for which the testing routine will select the frequency on its own.

MELT-AC-F setting is defined in Table 12.

#### Table 12: MELT-AC-F setting

| Signal frequency    | Range      | Configuration<br>settings |

|---------------------|------------|---------------------------|

| For active AC tests | 10 1000 Hz | 25 Hz                     |

#### 4.5.4 Pair Identification Tone Frequency (MELT-PIT-F)

Parameter MELT-PIT-F sets up frequency of the pair identification tone. The supported set of frequencies is at the vendor's discretion.

MELT-PIT -F setting is defined in Table 13.

#### Table 13: MELT-PIT-F setting

|                                           | Range       | Configuration<br>settings |

|-------------------------------------------|-------------|---------------------------|

| Frequency of the pair identification tone | 300 3400 Hz | 800 Hz                    |

#### 4.5.5 Maximum Far-end Signature Conduction Voltage (MELT-MAXFE-SCV)

Parameter MELT-MAXFE-SCV specifies the maximum conduction voltage level of an expected far-end signature.

MELT-MAXFE-SCV setting is defined in Table 14.

#### Table 14: MELT-MAXFE-SCV setting

|                                                         | Range  | Configuration<br>settings |

|---------------------------------------------------------|--------|---------------------------|

| Maximum conduction voltage level of a far-end signature | 0 50 V | 20 V                      |

#### 4.5.6 Minimum Far-end Signature Conduction Voltage (MELT-MINFE-SCV)

Parameter MELT-MINFE-SCV specifies the minimum conduction voltage level of an expected far-end signature.

MELT-MINFE-SCV setting is defined in Table 15.

#### Table 15: MELT-MINFE-SCV setting

|                                                         | Range  | Configuration<br>settings |

|---------------------------------------------------------|--------|---------------------------|

| Minimum conduction voltage level of a far-end signature | 0 50 V | 6 V                       |

#### 4.6 MELT-P configuration parameters

This section describes the configuration parameters of the MELT-P function. When validating the system under test, the configurable parameters should be set to the values listed as "Configuration settings" in the following tables.

#### 4.6.1 Loop resistance classification threshold (MELT-LRC-TH)

Parameter MELT-LRC-TH defines the limit values for classification of the resistances to GND of the loop under test.

MELT-LRC-TH setting is defined in Table 16.

#### Table 16: MELT-LRC-TH setting

| Resistance to GND                             | Configuration<br>settings |

|-----------------------------------------------|---------------------------|

| Maximum resistance for a short-circuit to GND | 1.4 kΩ                    |

| Minimum resistance for a leakage to GND       | 150 kΩ                    |

| Maximum resistance for a leakage to GND       | 1500 kΩ                   |

#### 4.6.2 Loop parameters per unit length (MELT-LOOP-PARAMS)

MELT-LOOP-PARAMS defines the set of characteristic parameters necessary to determine length or distance information of the loop under test.

MELT-LOOP-PARAMS setting is defined in Table 17.

Table 17: MELT-LOOP-PARAMS setting

| Cable parameters per unit length     | Range       | Configuration<br>settings |

|--------------------------------------|-------------|---------------------------|

| Capacitance between tip and ring     | 0 100 nF/km | 12 nF/km                  |

| Capacitance between tip/ring and GND | 0 100 nF/km | 60 nF/km                  |

| DC resistance (sum of both wires)    | 50 400 Ω/km | 280 Ω/km                  |

#### 4.6.3 Hazardous DC voltage level (MELT-HDCV-L)

MELT-HDCV-L defines the level above which DC voltage SHALL be identified as hazardous.

MELT-HDCV-L setting is defined in Table 18.

#### Table 18: MELT-HDCV-L setting

|                      | Range   | Configuration<br>settings |

|----------------------|---------|---------------------------|

| Hazardous DC voltage | 0 200 V | 120 V                     |

#### 4.6.4 Hazardous AC voltage level (MELT-HACV-L)

MELT-HACV-L defines the level above which AC voltage SHALL be identified as hazardous.

MELT-HACV-L setting is defined in Table 19.

#### Table 19: MELT-HACV-L setting

|                      | Range      | Configuration<br>settings |

|----------------------|------------|---------------------------|

| Hazardous AC voltage | 0 200 Vrms | 50 Vrms                   |

#### 4.6.5 Foreign EMF DC voltage level (MELT-FDCV-L)

MELT-FDCV-L defines the level above which DC voltage SHALL be identified as a foreign EMF.

MELT-FDCV-L setting is defined in Table 20.

#### Table 20: MELT-FDCV-L setting

|                        | Range  | Configuration<br>settings |

|------------------------|--------|---------------------------|

| Foreign EMF DC voltage | 0 50 V | 6 V                       |

#### 4.6.6 Foreign EMF AC voltage level (MELT-FACV-L)

MELT-FACV-L defines the level above which AC voltage SHALL be identified as a foreign EMF.

MELT-FACV-L setting is defined in Table 21.

Table 21: MELT-FACV-L setting

|                        | Range     | Configuration<br>settings |

|------------------------|-----------|---------------------------|

| Foreign EMF AC voltage | 0 50 Vrms | 10 Vrms                   |

#### 4.6.7 System capacitance at the CPE side (MELT-SYSC-CPE)

MELT-SYSC-CPE defines the expected value of the system capacitance at the CPE side as it appears in parallel between tip and ring in a corresponding MELT measurement.

MEL-SYSC-CPE setting is defined in Table 22.

#### Table 22: MELT- SYSC-CPE setting

| System capacitance at the CPE side | Range  | Configuration<br>settings |

|------------------------------------|--------|---------------------------|

| VDSL2, ADSL2/2plus                 | 0 2 μF | 27 nF                     |

| SHDSL                              | 02μF   | 1 μF                      |

## 5 MELT-PMD Testing

#### 5.1 MELT-PMD Test Cases for Measurement Functions

#### 5.1.1 The 4-Element DC Resistance

#### 5.1.1.1 Measurement of the 4-element DC resistance with a controlled metallic voltage

Test procedure for measurement of the 4-element DC resistance with a controlled metallic voltage is defined in Table 23.

|               | Table 23: 4-element DC resistance measurement                                                                         |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| Test          | (1)See Figure 1 for the test setup.                                                                                   |

| Configuration | (2)See Section 4.4.1 for definition of the test resistors. Each test resistor SHALL meet tolerance limits of Table 2. |

|               | (3)See Section 5.1.1.2 for accuracy requirements of the DC test voltages and currents.                                |

|               | (4)Set DSL port to IDLE.                                                                                              |

| Method of     | (1)Connect resistor R1 of Table 2 between RING and TIP.                                                               |

| Procedure     | (2)Perform MELT measurement.                                                                                          |

|               | (3)Record the reported results of the MELT measurement.                                                               |

|               | (4)Connect resistor R1 between RING and GND.                                                                          |

|               | (5)Perform MELT measurement.                                                                                          |

|               | (6)Record the reported results of the MELT measurement.                                                               |

|               | (7)Connect resistor R1 between TIP and GND.                                                                           |

|               | (8)Perform MELT measurement.                                                                                          |

|               | (9)Record the reported results of the MELT measurement.                                                               |

|               | (10)Repeat step (1) to (9) using all other test resistors of Table 2 (R2, R3,, R12).                                  |

|               | (11)Connect resistor R13 of Table 6 between RING and TIP (open loop).                                                 |

|               | (12)Perform MELT measurement.                                                                                         |

|               | (13)Record the reported results of the MELT measurement.                                                              |

|               |                                                                                                                       |

Table 23: 4-element DC resistance measurement

| Expected<br>Result | (1) MELT measurement SHALL be performed in less than 20 seconds, as defined in Section E.1.1/G.996.2 [5].                                                                                                                                         |

|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | (2) Measured resistance values R <sub>TR</sub> , R <sub>RT</sub> , R <sub>TG</sub> and R <sub>RG</sub> SHALL meet the accuracy limits defined in Table E.1/G.996.2, after adding the multimeter tolerance values defined in Table 2. <sup>1</sup> |

|                    | (3) Measured resistance values SHALL be in the range of 0 to 10 M $\Omega$ with a granularity of 1 $\Omega$ (Section E.2.3.1/G.996.2) (NOTE1).                                                                                                    |

|                    | (4) Reported voltage values $VDC_{TR}$ , $VDC_{RT}$ , $VDC_{TG}$ and $VDC_{RG}$<br>SHOULD meet the requirement of Section 5.1.1.2 (NOTE2).                                                                                                        |

|                    | (5) Reported current values $IDC_{TR}$ , $IDC_{RT}$ , $IDC_{TG}$ and $IDC_{RG}$ SHOULD meet the requirement of Section 5.1.1.2 (NOTE3).                                                                                                           |

|                    | se of an open loop (R13) measured resistance values ( $R_{TR}$ , $R_{RG}$ and $R_{TG}$ )<br>M $\Omega$ SHALL be limited to 10M $\Omega$ .                                                                                                         |

|                    | e time of publication of TR-286 the accuracy requirements for the test $T_{R}$ , $VDC_{RT}$ , $VDC_{TG}$ and $VDC_{RG}$ were for further study in G.996.2.                                                                                        |

|                    | e time of publication of TR-286 the accuracy requirements for the test $_{R}$ , $IDC_{RT}$ , $IDC_{TG}$ and $IDC_{RG}$ were for further study in G.996.2.                                                                                         |

|                    | esting procedure will return values for the $R_{TR}$ , $R_{RT}$ , $R_{TG}$ , and $R_{RG}$ branches                                                                                                                                                |

even if only one branch has a test load and the others are left open. The result obtained for the branch containing the test load SHALL be compared with the test load measurement from the multimeter. The other results SHALL be ignored.

## 5.1.1.2 Test voltage and current in the measurement of the 4-element DC resistance with controlled metallic voltage

Test voltages ( $VDC_{TR}$ ,  $VDC_{RT}$ ,  $VDC_{TG}$  and  $VDC_{RG}$ ) and test currents ( $IDC_{TR}$ ,  $IDC_{RT}$ ,  $IDC_{TG}$  and  $IDC_{RG}$ ) for the measurement of the 4-element DC resistance SHOULD be reported within accuracy limits defined in Table 24 and Table 25. Range of valid values and granularity are defined in Section E.2.3.2/G.996.2 and Section E.2.3.3/G.996.2.

The optional voltage values are returned by the procedure and represent voltages that were present at some instant of time during the test execution. In order to compare the reported values with the actual voltages, they will have to be monitored with an oscilloscope while the test is executing. Measuring them with a multimeter will not be possible.

The optional current values are an estimate of the current that would be measured by two ammeters connected tip-to-ground and ring-to-ground, or by one ammeter connected tip-to-ring. They are not current values that can be measured during the test execution.

#### Table 24: Test voltages in the 4-element DC resistance measurement

<sup>&</sup>lt;sup>1</sup> For example: if the required MELT accuracy is +/-5% and the multimeter accuracy is +/-1%, the overall required accuracy is +/-6%.

| Test voltage (V)            | Accuracy          | Granularity |

|-----------------------------|-------------------|-------------|

| $-20 \leq VDC_{XY} \leq 20$ | $\pm 1 \text{ V}$ | 100mV       |

| $-100 < VDC_{XY} < -20$     | $\pm$ 5 %         | 100mV       |

| $20 < VDC_{XY} < 100$       |                   |             |

#### Table 25: Test currents in the 4-element DC resistance measurement

| Test current (mA)         | Accuracy           | Granularity |

|---------------------------|--------------------|-------------|

| $-20 \le IDC_{XY} \le 20$ | $\pm 2 \text{ mA}$ | 1 μΑ        |

| $-100 < IDC_{XY} < -20$   | $\pm$ 10 %         | 1 µA        |

| $20 < IDC_{XY} < 100$     |                    |             |

### 5.1.2 The 3-Element Capacitance

#### 5.1.2.1 Measurement of the 3-element capacitance with a controlled metallic voltage

Test procedure for measurement of the 3-element capacitance with a controlled metallic voltage is defined in Table 26.

|               | Table 20. 3-element capacitance measurement                                                                                                |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| Test          | (1) See Figure 1 for the test setup.                                                                                                       |

| Configuration | <ul><li>(2) See Section 4.4.2 for definition of the test capacitors. Each test capacitor SHALL meet tolerance limits of Table 3.</li></ul> |

|               | (3) See Section 5.1.2.2 for accuracy requirements of the AC test voltages.                                                                 |

|               | (4) Set DSL port to IDLE.                                                                                                                  |

| Method of     | (1) Connect capacitor C1 of Table 3 between RING and TIP (open loop).                                                                      |

| Procedure     | (2) Perform MELT measurement.                                                                                                              |

|               | (3) Record the reported results of the MELT measurement.                                                                                   |

|               | (4) Connect capacitor C2 of Table 3 between RING and TIP.                                                                                  |

|               | (5) Perform MELT measurement.                                                                                                              |

|               | (6) Record the reported results of the MELT measurement.                                                                                   |

|               | (7) Connect capacitor C2 between RING and GND.                                                                                             |

|               | (8) Perform MELT measurement.                                                                                                              |

|               | (9) Record the reported results of the MELT measurement.                                                                                   |

|               | (10)Connect capacitor C2 between TIP and GND.                                                                                              |

|               | (11)Perform MELT measurement.                                                                                                              |

|               | (12)Record the reported results of the MELT measurement.                                                                                   |

|               | (13)Repeat step (4) to (12) using all other capacitors of Table 3 (C3, C4,,C8).                                                            |

| Expected<br>Result | (1) MELT measurement SHALL be performed in less than 20 seconds, as defined in Section E.1.1/G.996.2.                                                                                                                                                                                  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | (2) Measured capacitance values $C_{TR}$ , $C_{TG}$ and $C_{RG}$ SHALL meet the accuracy limits defined in Table E.2/G.996.2 and Table E.3/G.996.2 (for SHDSL, Table E.4/G.996.2 and Table E.5/G.996.2), after adding the multimeter tolerance values defined in Table 3. <sup>2</sup> |

|                    | (3) Measured capacitance values SHALL be in the range of 0 to 5 $\mu$ F with a granularity of 0.1nF (Section E.2.3.4/G.996.2) (NOTE1).                                                                                                                                                 |

|                    | (4) Reported voltage values $VAC_{TR-CC}$ , $VAC_{TG-CC}$ and $VAC_{RG-CC}$ and frequency SHOULD meet the requirement of Section 5.1.2.2 (NOTE2).                                                                                                                                      |

NOTE1: In case of an open loop (C1) measured capacitance values ( $C_{TR}$ ,  $C_{RG}$  and  $C_{TG}$ ) SHALL be 0nF  $\pm$  3nF. Negative results may be rounded to 0nF, see Section E.2.3.4/G.996.2.

NOTE2: At the time of publication of TR-286 the accuracy requirements for the test voltages  $VAC_{TR-CC}$ ,  $VAC_{TG-CC}$  and  $VAC_{RG-CC}$  were for further study in G.996.2.

NOTE3: The testing procedure will return values for the  $C_{TR}$ ,  $C_{TG}$ , and  $C_{RG}$  branches even if only one branch has a test load and the others are left open. The result obtained for the branch containing the test load SHALL be compared with the test load measured with the multimeter. The other results SHALL be ignored.

## 5.1.2.2 Test voltages in the 3-element capacitance test with a controlled metallic voltage

Test voltages ( $VAC_{TR-CC}$ ,  $VAC_{TG-CC}$  and  $VAC_{RG-CC}$ ) for the measurement of the 3-element capacitance (if performed with a sinewave signal) SHOULD be reported within accuracy limits defined in Table 27. Range of valid values and granularity are defined in Section E.2.3.11/G.996.2.

The optional voltage values are returned by the procedure and represent voltages that were present at some instant of time during the test execution. In order to compare the reported values with the actual voltages, they will have to be monitored with an oscilloscope while the test is executing. Measuring them with a multimeter will not be possible.

| Test voltage (Vrms)        | Accuracy       | Granularity |

|----------------------------|----------------|-------------|

| $0 \le VAC_{XY-CC} \le 10$ | $\pm 0.5$ Vrms | 100mV       |

| $10 < VAC_{XY-CC} < 100$   | ± 5 %          | 100mV       |

Table 27: Test voltages in the 3-element capacitance measurement

Range of valid values and granularity for the measurement frequency for a 3-element capacitance measurement, if performed with a sinewave signal, is from 10 to 1000Hz with a granularity of 1Hz, as defined in Section E.2.2.1/G.996.2.

#### 5.1.3 Measurement of foreign voltages

Test procedure for measurement of foreign DC voltage is defined in Table 28.

$<sup>^{2}</sup>$  For example, if the required MELT accuracy is +/-3nF and the multimeter accuracy is+/-1nF, the overall required accuracy is +/-4nF.

| Table 28: Foreign DC voltage measurement |                                                                                                                                                                                                                      |  |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Test                                     | (1) See Figure 1 for the test setup.                                                                                                                                                                                 |  |

| Configuration                            | <ul><li>(2) See Section 4.4.3 for definition of the foreign voltage DC sources<br/>(FVDC). Each FVDC source SHALL meet tolerance limits of Table 4.</li></ul>                                                        |  |

|                                          | (3) Set DSL port to IDLE.                                                                                                                                                                                            |  |

| Method of<br>Procedure                   | (1) Connect the foreign DC source between RING and TIP and generate voltage FVDC1 of Table 4 between RING and TIP (open loop).                                                                                       |  |

|                                          | (2) Perform MELT measurement.                                                                                                                                                                                        |  |

|                                          | (3) Record the reported results of the MELT measurement.                                                                                                                                                             |  |

|                                          | (4) Connect the foreign DC source between RING and TIP and generate voltage FVDC2 of Table 4.                                                                                                                        |  |

|                                          | (5) Perform MELT measurement.                                                                                                                                                                                        |  |

|                                          | (6) Record the reported results of the MELT measurement.                                                                                                                                                             |  |

|                                          | (7) Connect the foreign DC source between RING and GND and generate voltage FVDC2 of Table 4.                                                                                                                        |  |

|                                          | (8) Perform MELT measurement.                                                                                                                                                                                        |  |

|                                          | (9) Record the reported results of the MELT measurement.                                                                                                                                                             |  |

|                                          | (10)Connect the foreign DC source between TIP and GND and generate voltage FVDC2 of Table 4.                                                                                                                         |  |

|                                          | (11)Perform MELT measurement.                                                                                                                                                                                        |  |

|                                          | (12)Record the reported results of the MELT measurement.                                                                                                                                                             |  |

|                                          | (13)Repeat steps (4) to (12), for all other DC source voltages of Table 4 (FVDC3,, FVDC13).                                                                                                                          |  |

| Expected<br>Result                       | (1) MELT measurement SHALL be performed in less than 20 seconds, as defined in Section E.1.1/G.996.2.                                                                                                                |  |

|                                          | (2) Measured DC foreign voltage values $V_{TR,DC}$ , $V_{RG,DC}$ and $V_{TG,DC}$<br>SHALL meet the accuracy limits defined in Table E.6/G.996.2, after<br>adding the multimeter tolerance values defined in Table 4. |  |

|                                          | <ul><li>(3) Measured DC foreign voltage values SHALL be in the range of -350 to 350 V with a granularity of 0.1V (Section E.2.3.5/G.996.2) (NOTE1).</li></ul>                                                        |  |

|                                          | <ul><li>(4) Measured DC foreign voltage greater than MELT-HDCV-L (see<br/>Section 4.6.3) SHALL be declared as hazardous voltage.</li></ul>                                                                           |  |

| NOTE1: In case                           | of an open loop (FVDC1) measured foreign voltage values ( $V_{TRDC}$ , $V_{RGDC}$                                                                                                                                    |  |

Table 28: Foreign DC voltage measurement

NOTE1: In case of an open loop (FVDC1) measured foreign voltage values ( $V_{TR,DC}$ ,  $V_{RG,DC}$  and  $V_{TG,D}$ ) SHALL be 0V ±1V.

NOTE2: The testing procedure will return values for the  $V_{TR}$ ,  $V_{TG}$ , and  $V_{RG}$  branches even if only one branch has a voltage applied and the others are left open. The result obtained for the branch containing the voltage source SHALL be compared with the voltage measured with the multimeter. The other results SHALL be ignored. Because of the presence of protection components, it is possible that the source voltage be affected by the connection to the test circuit. The multimeter measurement of the applied voltage SHALL be performed during the execution of the testing procedure to compare it with the MELT result. Test procedure for measurement of foreign AC voltage and frequency is defined in Table 29.

|                        | able 29: Foreign AC voltage and frequency measurement                                                                                                                                                                    |

|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Test                   | (1) See Figure 1 for the test setup.                                                                                                                                                                                     |