# Parallel Computing Research at Illinois The UPCRC Agenda

Department of Computer Science Department of Electrical and Computer Engineering Coordinated Science Laboratory University of Illinois at Urbana-Champaign

# PARALLEL @ILLINOIS

# PARALLEL @ILLINOIS

# Parallel Computing Research at Illinois The UPCRC Agenda

Department of Computer Science Department of Electrical and Computer Engineering Coordinated Science Laboratory University of Illinois at Urbana-Champaign November 2008

Sarita V. Adve Vikram S. Adve Gul Agha Matthew I. Frank María Jesús Garzarán John C. Hart Wen-mei W. Hwu **Ralph E. Johnson** Laxmikant V. Kale **Rakesh Kumar** Darko Marinov Klara Nahrstedt David Padua Madhusudan Parthasarathy Sanjay J. Patel **Grigore Rosu** Dan Roth **Marc Snir Josep Torrellas Craig Zilles**

# Parallel@Illinois: Pioneering and Promoting Parallel Computing

Illinois history in parallel computing stretches more than 40 years. From the first academic parallel supercomputer, the ILLIAC IV started in 1964, to today's work to install the first petascale computer, Blue Waters, Illinois has defined the landscape of parallel computing. Contributions from past and current Illinois faculty include:

- ILLIAC

- CEDAR

- Illinois Cache Coherence (MESI) Protocol

- OpenMP

- MPI

- Path Pascal

- Actors

- Java and C++ memory models

- Compilers and auto-parallelization techniques—Analyzer, Polaris, Parafrase, IMPACT, LLVM

- Race detection techniques

- Parallel runtime systems—Chare Kernel, Charm++

- IBM/DARPA PERCS—a precursor to IBM's Power 7

- AVIO to detect atomicity violations

- Parallel programming patterns

Today, parallel computing at Illinois spans mobile and desktop client computing at the Universal Parallel Computing Research Center (UPCRC—**www.upcrc.illinois.edu**), cloud computing, and petascale supercomputing. The work includes long-term research, education, and one-of-a-kind testbed installation, including the world's largest academic supercomputer.

Excellence in parallel computing at Illinois is a collaborative effort that transcends disciplinary boundaries. The Coordinated Science Laboratory, Department of Computer Science, Department of Electrical and Computer Engineering, and the National Center for Supercomputing Applications (NCSA) work together and in conjunction with faculty and researchers across the entire campus, including chemists, biologists, artists, structural engineers, humanities experts, economists, and more.

Parallel@Illinois (**www.parallel.illinois.edu**) is the collective representation of Illinois' current efforts in parallel computing research and education. These include:

- Universal Parallel Computing Research Center

- Blue Waters

- Gigascale Systems Research Center

- Cloud Computing Testbed

- CUDA Center of Excellence

- Institute for Advanced Computing Applications and Technologies

- OpenSPARC Center of Excellence

# UPCRC Illinois Universal Parallel Computing Research Center

This paper represents the vision and research agenda of the Universal Parallel Computing Research Center at the University of Illinois at Urbana-Champaign. The UPCRC gratefully acknowledges the sponsorship of Intel and Microsoft Corporations for much of this research.

We would like to thank Bill Gropp, Mike Heath, and Jim Larus for their comments on this paper.

We welcome your feedback on this paper. Comments and suggestions can be sent to community@upcrc.illinois.edu or posted at www.upcrc.illinios.edu/whitepaper.html. An electronic version of this paper is also available at this URL.

Copyright © 2008 The Board of Trustees of the University of Illinois. All Rights Reserved.

# Contents

| 1   | Introduction      |                                                                        |  |  |

|-----|-------------------|------------------------------------------------------------------------|--|--|

| 2 0 |                   | <b>erview</b>                                                          |  |  |

|     | 2.1               | Applications and Patterns                                              |  |  |

|     | 2.2               | Disciplined Programming Models                                         |  |  |

|     | 2.3               | Development and Execution Environments                                 |  |  |

| 3   | Ар                | Applications and Patterns                                              |  |  |

|     | 3.1               | Applications                                                           |  |  |

|     |                   | 3.1.1 Dynamic Virtual Environments                                     |  |  |

|     |                   | 3.1.2 Natural Language Processing                                      |  |  |

|     |                   | 3.1.3 Tele-immersive Environments                                      |  |  |

|     | 3.2               | Patterns                                                               |  |  |

| 4   | Dis               | ciplined Programming Models                                            |  |  |

|     | 4.1               | Disciplined Shared Memory                                              |  |  |

|     | 4.2               | Parallel Operators                                                     |  |  |

|     | 4.3               | Metaprogramming and Autotuning                                         |  |  |

|     | 4.4               | Domain-Specific Environments                                           |  |  |

|     | 4.5               | Actors                                                                 |  |  |

| 5   | Dev               | velopment and Execution Environments                                   |  |  |

|     | 5.1               | Translation Environment                                                |  |  |

|     | 5.2               | Runtime System   32                                                    |  |  |

|     | 5.3               | Hardware Architecture                                                  |  |  |

|     |                   | 5.3.1 The Bulk Multicore: High-Performance, Programmable Shared Memory |  |  |

|     |                   | 5.3.2 DeNovo: Rethinking Hardware for Disciplined Parallelism          |  |  |

|     | 5.4               | Formal Methods and Tools to Check Correctness                          |  |  |

| 6   | Cor               | nclusions                                                              |  |  |

| Re  | <b>References</b> |                                                                        |  |  |

# **1** Introduction

For many decades, Moore's law has bestowed a wealth of transistors that hardware designers and compiler writers have converted to usable performance, without changing the sequential programming interface. The main techniques for these performance benefits—increased clock frequency and smarter but increasingly complex architectures—are now hitting the so-called power wall. The computer industry has accepted that future performance increases must largely come from increasing the number of processors (or cores) on a die, rather than making a single core go faster. This historic shift to multicore processors changes the programming interface by exposing parallelism to the programmer, after decades of sequential computing.

Parallelism has been successfully used in many domains such as high performance computing (HPC), servers, graphics accelerators, and many embedded systems. The multicore inflection point, however, affects the entire market, particularly the client space, where parallelism has not been previously widespread. Programs with millions of lines of code must be converted or rewritten to take advantage of parallelism; yet, as practiced today, parallel programming for the client is a difficult task performed by few programmers. Commonly used programming models are prone to subtle, hard to reproduce bugs, and parallel programs are notoriously hard to test due to data races, non-deterministic interleavings, and complex memory models. Mapping a parallel application to parallel hardware is also difficult given the large number of degrees of freedom (how many cores to use, whether to use special instructions or accelerators, etc.), and traditional parallel environments have done a poor job virtualizing the hardware for the programmer. As a result, only the highest performance seeking and skilled programmers have been exposed to parallel computing, resulting in little investment in development environments and a lack of trained manpower. There is a risk that while hardware races ahead to ever-larger numbers of cores, software will lag behind and few applications will leverage the potential hardware performance.

Moving forward, if every computer will be a parallel computer, most programs must execute in parallel and most programming teams must be able to develop parallel programs, a daunting goal given the above problems. Illinois has a rich history in parallel computing starting from the genesis of the field and continues a broad research program in parallel computing today [1]. This program includes the Universal Parallel Computing Research Center (UPCRC), established at Illinois by Intel and Microsoft, together with a sibling center established at Berkeley. These two centers are focused on the problems of multicore computing, especially in the client and mobile domains.

This paper describes the research vision and agenda for client and mobile computing research at Illinois, focusing on the activities at UPCRC (some of which preceded UPCRC).

Given the long history of parallel computing, it is natural to ask whether the challenges we face today differ from those of the past. Compared to the HPC and server markets, the traditional focus of parallel computing research, the client market brings new difficulties, but it also brings opportunities. Table 1 summarizes some of the key differences.

| НРС                      | Server                   | Client                  |

|--------------------------|--------------------------|-------------------------|

| Few applications         | Few subsystems           | All applications        |

| Very skilled programmers | Skilled programmers      | All programmers         |

| Latency                  | Throughput               | Quality of experience   |

| Deadline always missed   | Time to market important | Time to market critical |

| Small volume             | Medium volume            | Large volume            |

**TABLE 1** • Client parallel computing versus high performance and server computing.

The parallel client system must enable most programming teams to write "good" parallel code. In contrast to the HPC and server markets, the metrics for "goodness" are more diverse. Client programmers care about many *performance* metrics, including execution time, power consumption, audio and video quality, output accuracy, and availability, all which contribute to the ultimate metric—the quality of user experience. The programmers and system vendors also care about *scalability*—using more cores should improve quality of experience, with no software rewrite. Time to market, and hence software development *productivity*, is paramount. Fortunately, the volume is much larger than the HPC and server markets, affording investments on a scale not previously possible.

A key impediment to all three goals of performance, scalability, and productivity is the lack of high-level parallel programming models. To make parallelism truly universal, we must move beyond current bug-prone parallel programming models to an ecosystem that reduces opportunities for errors, while exploiting the full performance potential of parallelism. We are optimistic that this is possible for two reasons. First, although current practices make parallel programming hard, our view is that this is not a fundamental property of all parallelism. For example, at Illinois, middle school students routinely write parallel programs using the Smalltalk-based graphic language, Squeak, without being aware that parallelism is supposed to be hard [2]. The lesson here is that we need to provide the right form of parallelism for the right problem and the right set of tools to support it. While some parallel codes may inherently require complex, bug-prone interactions among threads, many parallel programs will have interactions with a simple logic and should be provided a programming notation that expresses this logic in a clear way. Our second reason for optimism arises from the observation that the high market volumes on the client side can support multiple programming solutions that can shed the burdens of a one-size-fits-all solution; further, these markets can afford investments in sophisticated development tools and execution environments that can be translated to simpler programming models for the programmer.

Our research agenda therefore centers on the following three themes.

#### • Focus on Disciplined Parallel Programming.

Modern sequential programming languages have evolved from unstructured programs with goto statements to structured procedural languages to object-oriented languages. Notions of encapsulation and modularity make sequential programming easier by promoting a separation of concerns, both in terms of correctness and performance. Further, modern notions of safety simplify programming by restricting the set of possible dynamic interactions. In comparison to these advances in sequential languages, threads programming is still in the "go-to" age [3]. We therefore aim to develop *disciplined parallel programming models and languages, supported by sophisticated development and execution environments,* that will offer the analog of modern sequential programming principles of safety, structure, and separation of concerns.

#### Multi-Front Attack on Multicore Programming.

Illinois has a long history of work on parallelism at all levels from applications and programming abstractions down to hardware architecture, and across a broad spectrum of approaches from explicit high-performance programming to automatic tools that hide the details of parallelism. Our focus on disciplined parallelism is backed up by a broad-based attack that uses every weapon in our arsenal to address this problem. We investigate disciplined explicitly parallel languages, metaprogramming and autotuners, and domain-specific environments. Leveraging our strength in compilers, we aim for a powerful translation environment to exploit information from multiple sources (language level annotations, compiler analyses, runtime, and hardware) at different times in the life of a program. Following decades of parallel architecture research, we propose novel multicore hardware substrates that not only enable performance scalability but also support programmability. Finally, our work with refactoring tools will help move existing code to our new environments, and formal methods based techniques and tools will help ensure correctness.

#### • Human-Centric Vision of Future Consumer Applications.

Our work is driven by a foreseeable future where all client applications will be parallel, and the primary consumer feature that will drive the economics of future client software development will be the quality of the human interaction. We are targeting applications that rely on enabling technologies for computer support of social interaction through quantum-leaps in immersive visual realism, reliable natural-language processing, and robust teleprescence. Investigating these applications reveals new approaches to parallel pattern analysis, inspires new multicore versions of domain-specific environments, and serves as a testbed for evaluating, refining and ultimately proving our ideas on multicore programming.

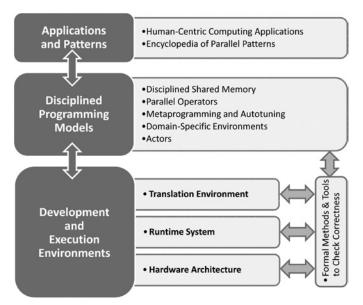

This section gives an overview of our agenda for parallel applications and patterns, disciplined parallel programming models, and development and execution environments, summarized in Figure 1. Subsequent sections describe our projects in more detail.

FIGURE 1 • Overview of the UPCRC/Illinois research agenda.

# 2.1 Applications and Patterns

The long history of parallel computing at Illinois is as much a history of parallel applications as of parallel systems. As we move to parallelism in the client, we continue our previously successful research model of integrated teams of applications and systems researchers. Specifically, the following experiences and observations drive our work on future client applications.

• Integrating applications and systems research: Systems with new capabilities drive new applications and new applications drive new systems. Parallel computing research at Illinois has repeatedly bootstrapped this cycle with integrated applications and systems research, in areas ranging from conventional high performance computing to more recent efforts in the general purpose GPU (GPGPU) domain. For example, 15% and 20% of the cycles in one year at NCSA and the Pittsburgh Supercomputing Center respectively ran applications (including NAMD [4, 5]) using Charm++ [6], co-developed by one of us. The evolution of Charm++ is a clear demonstration of how application research can drive the language/ runtime research agenda, leading to techniques that in turn are useful for a broader set of applications.

Illinois is also recognized as an early innovator and leading center in exploiting the 100+ cores on a GPU for diverse applications ranging from graphics to simulation to more general-purpose domains [7, 8, 9, 10]. Our client computing research agenda continues this tradition. A group of applications researchers from representative client domains are working closely with systems researchers to produce parallelized frameworks that represent key computations in these domains. This process will provide a testbed for and influence our systems research ideas. As the systems ideas mature, the application frameworks will evolve to use them to add new value for the applications and will be disseminated for a wider community of application developers.

- Human-centric computing will drive multicore client applications: For our research to be relevant, it is imperative that it be driven by the client computing workloads of the future. These workloads will be CPU intensive and will require computing at a fast client rather than in the "cloud." We believe that such workloads abound—many of them will have a central theme of understanding humans and facilitating their interactions with other humans and with large amounts of information. Understanding and reacting to the (human) client's needs in real-time, with enough realism, within the current context, and without sacrificing privacy has the potential to absorb foreseeable client-side performance increases. Society will determine the next generation of killer applications. We aim to accelerate their development by focusing on a few broad domains that we believe encompass the "killer technologies" for them, and for which we have leading in-house expertise.

- *Parallel patterns as a vocabulary for developers:* Before programmers start using our programming models and tools, they must think about the parallel algorithms, data structures, and more specifically, parallel *patterns* to use for their applications. We believe a vocabulary of such patterns is essential to educate parallel programmers, both directly and by enabling sharing of experiences. One of us previously co-authored a book on design patterns for object-oriented programming that many believe to be the engine that popularized sequential object-oriented programming [11]. That effort focused on very specific patterns that programmers could directly use to translate to code. We aim to duplicate that success for parallel programming. For a few years, we have been working to catalog parallel patterns through a community effort, previously in the context of high performance computing [12] and now broadened to include client computing. Like the sequential patterns book, we believe that the most value in a parallel patterns catalog will come from cataloging the rich diversity of specific patterns that programmers can directly use in their code. This is in contrast to identifying a few motifs, which is useful as a characterization of important computations but has unclear value in guiding code development.

Motivated by the above observations and experiences, we are engaged in two types of activities:

- 1) Domain-specific frameworks and APIs: We have identified three important domains for future killer client applications:

- a. Dynamic virtual environments

- b. Natural language processing

- c. Tele-immersive environments

These domains cover technologies in graphics, computer vision, and image, video, text, and speech processing. Leading researchers from these areas are collaborating with systems researchers to define and implement parallelized, high-performance domain-specific frameworks and APIs for key computations in the above domains, using the technologies developed by our systems researchers.

2) Parallel Patterns: We are engaged in an effort to create an encyclopedia of parallel patterns that encompasses a broad set of programmer experiences. This is necessarily a community effort. It involves collaboration with programmers inside and outside our university and other researchers also working on parallel patterns. To facilitate this collaboration, we plan a workshop series on parallel patterns, based on similar workshops we have organized in the past [12].

# 2.2 Disciplined Programming Models

Three observations drive our work on disciplined parallel programming models:

- Disciplined coordination: In a seminal paper [3], Dijkstra argued that goto's make programs hard to comprehend and debug since, when they are used, there is no easy way to describe the mapping from the static structure of the code to the dynamic evolution of the execution. Arbitrarily placed task spawns, unsynchronized conflicting memory accesses or data races, and low-level synchronization operations such as locks, are the equivalent of goto's in the parallel world: it is hard to describe the mapping from the individual executions of threads to the global execution. We seek models that impose structure on parallel control flow and on synchronization. Current language specifications already discourage the use of data races [13, 14], but do not aid the programmer in achieving this goal. A stronger guarantee is *determinism*, which guarantees that for a given input, the program will always produce the same output. This output is the result of an equivalent sequential execution, providing a simple semantic model. This model facilitates code development and debugging, while still exposing to the programmer a parallel performance model. Effectively, deterministic languages can ride on the advances in sequential programming, including safety, modularity, and composability. Many programs, especially a large class of transformative programs, are deterministic; however, current languages do not aid in expressing them in provably deterministic terms. We wish to explore the extent to which language support can be used to guarantee data-race-freedom, determinism, and other higher level coordination structures, in the context of modern sequential programming practices and client applications.

- **Encapsulation:** Not all code will be deterministic—reactive programs and some classes of transformative programs require various forms of non-determinism for efficiency. For a disciplined environment, we propose that when non-deterministic behavior is unavoidable, it be made explicit and encapsulated in a way that limits its impact on the rest of the program. Actor models, where the interaction between sequential threads is always explicit, are an example of such an approach that works well for reactive programs. How to best encapsulate non-determinism for transformative programs and how to specify alternate disciplines for non-determinism (other than data-race-free) are research questions we are currently exploring.

- Enabling performance through a separation of concerns: As mentioned previously, discipline is not an end in itself, but a means to exploiting the potential of parallelism. In another influential paper [15], Dijkstra articulated the notion of separation of concerns that allows reasoning about one property of a program (e.g., correctness) without having to simultaneously reason about another property (e.g., performance). In today's multicore environments, however, reasoning about correctness is intricately tied to reasoning about performance. The complexity of modern hardware means that much of this performance tuning

requires reasoning about complex (and often machine-specific) effects and subtle interactions. A key aspect of our work on disciplined models is to enable programmers to use higher levels of abstraction to specify functionality, while the system exploits this information to use its full flexibility to provide performance. Ideally, we would like to reduce the burden on programmers so they worry only about correctness while the system automatically tunes for performance.

The above observations motivate the following five specific research directions we are currently exploring.

- 1) Languages for disciplined shared memory: We are working on a general-purpose disciplined shared-memory language that builds upon modern object-oriented languages with strong safety properties, providing the programmer with all the familiar ease-of-use facilities of modern sequential languages in conjunction with disciplined parallelism. The general philosophy is to use language constructs, potentially backed up by the compiler, formal correctness checking tools, and hardware, to (i) guarantee no data races, (ii) guarantee determinism where possible, and (iii) where non-determinism is unavoidable, make it explicit and encapsulated with limited impact on the rest of the program [16, 17, 18]. This language would support both task-parallel and flexible data-parallel programming idioms, within a familiar object-oriented language. We aim to separate, to the extent possible, concerns about the semantics of programs from concerns about performance such as optimizations for locality. Such a language would support a progressive refinement of codes for performance tuning that does not affect the program semantics.

- 2) Parallel operators: Parallelism is most easily managed when it is encapsulated in operators defined on data aggregates (data parallelism) or simple iteration domains. Parallelism is hidden, thus facilitating program development and mapping to the target machine. Such operators also help raise the level of abstraction and thus have the potential of improving the quality of automatic optimization. Array operations have been used to represent parallel computations practically from the beginning of parallel computing, but modern client applications demand a richer set of array operations and extensions to irregular data structures such as sets and graphs; e.g., [19, 20, 21]. We are working to identify operators that would best serve our application domains. These operators can be added to existing programming languages or to newly developed disciplined shared memory languages. This work bridges the gap between general-purpose programming languages and domain-specific languages.

- **3)** *Metaprogramming and autotuning:* The idea with metaprogramming and autotuning is for the programmer to provide options for achieving the required functionality (e.g., different sorting algorithms). The system then automatically finds the best option for the current platform and (possibly) the current input, and generates this (close to) optimal program [22, 23, 24]. This line of work is further facilitated by identifying commonly used high-level data parallel primitive operations (e.g., [19, 20],) and *codelets* that can then be easily autotuned.

- 4) Domain-specific environments (DSEs): Domain-specific environments (including languages, libraries, and frameworks) can hide or significantly simplify the use of parallelism through the knowledge of domain information, and offer a high level of abstraction for the domain expert. Our research goal is not to create specific DSEs for each domain per se, but to provide the techniques and tools that domain experts for a wide range of domains can use to build effective parallel DSEs. Two examples we are working on are techniques to translate performance information into domain-specific terms and techniques to simplify the porting and evolution of applications to parallel domain-specific libraries and frameworks.

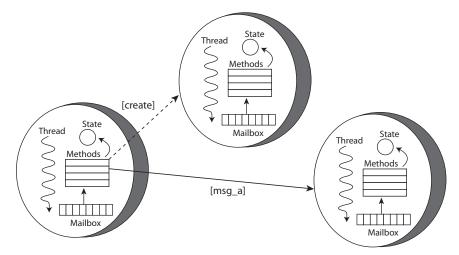

5) Actors: In many cases, shared memory and deterministic sequential reasoning are unnatural. Such cases include *programming in the large* such as cloud computing and sensor networks, and reactive programs, where concurrency is part of the problem specification. For such programs, we are exploring the actor model of computation [25]. Fine-grained actor languages have previously been shown to be efficiently implementable on distributed memory architectures [26]. Our focus here will be again driven by the separation of concerns philosophy—how to separate the specification of functional behavior of individual actors and the specification of aggregate multi-actor constraints such as scheduling, synchronization, quality of service, reliability, etc. [27, 28].

*In summary,* we hypothesize that to achieve the benefits of parallel computing, we will need disciplined programming models. Our research agenda involves an exploration of the appropriate disciplines such as data race freedom, determinism, controlled non-determinism, high-level operators, domain-specific encapsulation, metaprogramming, and actors. Although our eventual goal is for low-level programming to be needed only as a matter of last resort for the most performance-critical operations, realistically, we expect that software using current models and low-level programming will continue to exist for a number of years—our research agenda includes how to support such software with the best performance and with limited impact on correctness of the rest of the code. The fact that our agenda includes multiple approaches should not be surprising—it is analogous to the sequential world where programmers program at different levels of abstraction, including high-level domain-specific languages such as Mathematica, scripting languages such as Python, Java, C#, C++, C, and assembly.

## 2.3 Development and Execution Environments

The following observations drive our research in development and execution environments.

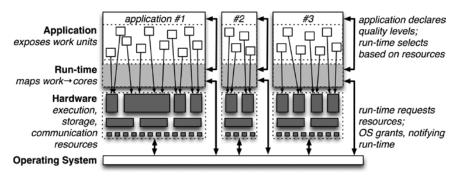

- **Supporting discipline:** New programming models require support from the system. For example, disciplined use of shared memory could benefit from hardware support for race detection [29] and for speculation [30, 31]. To truly separate performance concerns from correctness, and to support portability and scalability, it is likely that the runtime will need to expose a common virtual parallel interface as a target for the compiler and then map that interface to the current hardware at execution time. Autotuning and efficient run-time resource management require better performance sensors and actuators; e.g., for memory subsystem behavior.

- **Rewarding discipline:** Our research goes further than providing only the support required to enable our disciplined models. Too often, information available at higher levels of the system stack is lost at the lower levels, forgoing significant opportunities. All of our disciplined programming models naturally capture a rich amount of information about the program. Our research seeks to exploit this information to the fullest so we can reward discipline with robust performance, and foster the adoption of such models. For example, how can compilers use domain information from domain-specific frameworks and library components of a larger full application? How can high-level QoS specifications be used to drive runtime resource management? How can hardware exploit the fact that a program is written in a deterministic language to eliminate unnecessary traffic and complexity implied by current cache coherence protocols? More generally, if most code follows disciplined models, what concurrency model should hardware support?

- *Facilitating transition to disciplined programs:* Change is always disruptive, even change for the better. We can accelerate change by lowering its cost. Tools such as refactoring tools and correctness checking tools can make it easier to adopt our techniques; e.g., by enabling *interactive* (semi-automated) conversion of old code into the new models and by making it possible to use the new models with the old. Moreover, architectural support for deterministic replay of parallel programs [32, 33], data-race detection [29] and pervasive program monitoring [34, 35] will facilitate the transition of users to the new environments.

- **Supporting co-existence:** New programming models and new runtime environments will need to co-exist with currently available software for many years. Although we want to reward discipline, we cannot punish current software stacks. We therefore need to continue to provide performance and aid programmability with current programming models.

Driven by the above, we are engaged in the following research.

- Translation environment: We are working on an ambitious compiler infrastructure to enable our vision of disciplined parallel programming. Our compiler aims to bring together a number of transformations and analyses that exploit novel sources of information at various times in the life of an application, with the following goals: (i) to support explicitly parallel deterministic languages, high-level parallel operators, and domain-specific languages, exploiting the rich information provided by the programmer in these environments; (ii) to support parallelism discovery and speculation when the above information is insufficient or requires runtime speculation for validation; (iii) to appropriately interface with autotuners; and (iv) to support user-driven refactoring tools to enable porting existing sequential and parallel code to the new models.

- 2) Runtime system: The runtime system is responsible for virtualizing the (potentially heterogeneous) hardware for the rest of the software stack. Consequently, it is responsible for providing transparent resource management for potentially heterogeneous platforms, achieving required QoS within given physical constraints. Although we present the runtime and hardware as separate entities here, our research views the boundary between these two layers as fuzzy—techniques such as virtual instruction set computing [36, 37] and binary translation can replace a hardware interface with a software interface. We expect that virtualization, portability, and efficient handling of heterogeneity will increasingly require the kind of hardware-software co-design represented by such methods.

- 3) Hardware architecture: Our research in hardware architecture focuses not just on performance but on programmability as a first order design objective. We are working on two broad projects. The first project focuses on supporting a flexible substrate with scalable cache coherence, high-performance sequential memory consistency, and an easy-to-use development and debugging environment. The second project rethinks concurrent hardware as a co-designed component of our disciplined programming strategy, both for enforcing the discipline and for exploiting it for simpler and more efficient hardware.

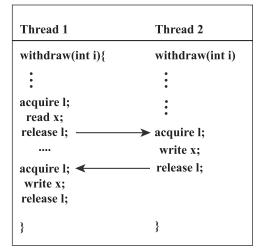

- 4) Formal methods and tools to check correctness: We are working on formal methods and tools for assuring correctness in concurrent programs. Our work encompasses the following research directions: (i) to understand high-level synchronization intentions that programmers use to manage concurrency, through the study of concurrency bug databases and user studies, (ii) utilizing the high-level intentions as specifications for testing concurrent programs, in particular to build effective algorithms that avoid enumerating and testing all interleavings, but find errors by testing only those interleavings that violate

these intentions, and (iii) to build mechanisms to sandbox the parts of a program that use undisciplined concurrency mechanisms and interface it with other portions that adhere to disciplined principles, and realize ways to summarize effects of these portions to infer correctness properties of the entire program.

# 3.1 Applications

Our applications thrust has two objectives: (1) to serve as a driver for our work in parallel programming models and environments, and (2) to apply state-of-the-art parallelization techniques to key application domains to accelerate the development of killer applications for multicore client systems. Our focus is on applications that enhance human/human and human/computer interactions, and particularly on the underlying compute intensive algorithms that improve interface intelligence and interactivity. Our current focus is in three broad domains: dynamic virtual environments, natural language processing, and tele-immersive environments.

Broadly, our approach within each domain is to develop a set of key parallelized frameworks that can be used by application developers to develop applications on a larger scale. Such frameworks will include APIs for frequently-used, compute-intensive functionality with extensibility for user-supplied kernels and data structures. The frameworks themselves will utilize technology developed in our other thrusts, such as autotuning and metaprogramming, and benefit from the parallel models and environments we are investigating. The subsequent subsections describe the individual application domains.

#### 3.1.1 Dynamic Virtual Environments

Real-time online virtual worlds (e.g. World of Warcraft and Second Life) have transformed the internet into an immersive space for social interaction, but the visuals and simulations of these online collaborative environments lag well behind those of stand-alone video games. Modern video games (like Halo 3) achieve cinematic photorealism and fluid motion by limiting the set of viewpoints and configurations of the game environment, and precomputing its lighting and animation over this limited set (via, e.g., the GPU-assisted precomputed radiance transfer used in the Xbox 360 [38]), essentially encoding the visuals into a massive high-dimensional multiple-viewpoint movie. This precomputation requires careful gameplay coordination (which makes game development expensive and time consuming), and does not support user interaction (e.g., building in an online virtual environment). The increased computational power of future multicore processors can overcome the need for precomputation, making videogames cheaper and faster to produce and online virtual environments more realistic.

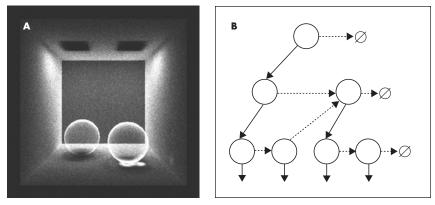

The performance of the rendering and simulation of online virtual worlds and video game environments relies on spatial data structures (SDS) to efficiently manage interactions between objects and neighborhood queries (as demonstrated in Figure 2a), and the fundamental challenge for multicore processing of these visual applications will be the development of efficient parallel algorithms for processing a shared spatial data structure. We and others have developed hierarchical SDS traversal algorithms that avoid conditional program flow for efficient streaming SIMD execution, as demonstrated in Figure 2b [39, 40]. We and others have also utilized parallel "scan" primitives to construct a balanced hierarchical SDS [41, 42]. But to achieve a goal of realistic rendering and animation of fully dynamic user-reconfigurable virtual worlds, we will need new multicore algorithms to efficiently maintain a kinetic SDS with efficient insertion, deletion, motion, and rebalancing.

**FIGURE 2** • (a) The performance of many visual applications relies on efficient nearest-neighbor queries, e.g. the photon-mapping rendering method determines the light reflected by a surface point by finding the k nearest photons. (b) A binary tree where each node contains two pointers: a "pass" pointer to the first child and a "fail" pointer to the next sibling (or uncle). This binary tree avoids conditional program flow since a node's traversal always follows one of its two nodes, supporting efficient SIMD parallel queries.

A natural application driver for client multicores therefore is a parallel framework for such spatial data structures that provides the applications developer with highly scalable SDS functionality for their applications. The interactivity demands of visual applications have resulted in a wide variety of detailed algorithms and data structures for managing spatial queries. Depending on the spatial data distribution, application, query type and processing architecture, the spatial data structure can be a 3-D grid, either simple or hashed, or a hierarchy, organized as an oct- tree, k-d tree, or BSP tree, and their processing can be organized iteratively or recursively, using SIMD operators, *short stacks*, or tree threading. As such, these domain-dependent application demands will be used to close-the-loop between our work on higher-level parallel pattern analysis and lower-level multicore implementation details.

#### 3.1.2 Natural Language Processing

Recent studies have shown that over 85% of the information that corporations handle is *unstructured*, the vast majority of which is textual. A multitude of techniques has to be used in order to enable intelligent access to this information and to support transforming it to forms that allow sensible use of the information. The fundamental issues that all these techniques have to address is that of semantics—if one wants to access text based on its content (rather than just *words* mentioned in it), there is a need to move toward *understanding* the text at an appropriate level. This may include understanding the topic of the text, the events described in it, the sentiments expressed in it, understanding "who is doing what to whom?", etc.

While there has been huge progress in research in these directions over the last few years, all commercial applications (e.g., Google, Yahoo, Microsoft, and others) make use of very shallow techniques—key words that are present in the text. One of the key reasons for that is computational—supporting semantic analysis of text, even at the level of a single sentence or a single paragraph, may take *seconds* on a single core machine.

Analyzing huge amounts of data, as is required to support better search, information extraction, and other deeper analyses of text, is therefore infeasible. Over the last few years, we have developed several algorithms and systems that support deeper analysis of natural language [43, 44, 45, 46, 47, 48, 49] that can serve as a basis for the current research.

Our work focuses on techniques for parallelizing natural language processing, and constructing a parallelized Natural Language Processing (NLP) framework for developers to create large-scale NLP-based applications. This involves creating parallelized functionality for optimization based machine learning (very high dimensional vector operations), constrained optimization based inference (including integer linear programming), and a large number of sub-graph isomorphism-like computations. Parallelizing can be done at multiple levels—from data parallel, to decomposing processes to independent threads to algorithmic innovations that would facilitate more efficient learning and constrained optimization algorithms in very high dimensions.

We foresee NLP-based applications that are server-based and those that are client-centric. Client-side applications include smart language translation in mobile devices, intelligent application user interfaces, and human-like interfaces to virtual characters. Client-side applications demand real-time and interactive performance, thus placing stringent performance demands on the underlying implementations, creating an excellent driver application for our parallelization technologies.

#### 3.1.3 Tele-immersive Environments

Future human-human communications can be dramatically enhanced with video environments that enable people to virtually interact together [50, 51, 52]. Our efforts in tele-immersive environments tap into long-standing world-class expertise at Illinois in video and image processing, computer vision, and multimedia systems. We are applying our parallelism technologies to state-of-the-art algorithms for 3D reconstruction, view synthesis, depth calculation, and super-resolution, all of which are computationally intensive and need to hit real-time performance thresholds.

One such example involves parallelization of 3D reconstruction algorithms, which are well known in the computer vision domain. Most 3D algorithms were designed for correctness to derive one 3D image from multiple 2D images and less importance was given to the real-time execution of the 3D algorithms. With the advent of 3D displays and 3D video cameras, 3D reconstruction algorithms must work in real-time; if one wants to achieve high-definition quality of video in spatial (HDTV quality) and temporal dimensions (30-60 frames per second), the 3D video algorithms must employ parallelism. Currently, most of the 3D cameras yield unsatisfactory results. They provide either 15-20 frames per second with very small frames (320-240) pixels or 8-10 frames per second with larger frames (640x480) and are not even close to the performance of HDTV video streaming with frame size of (1920x1080) pixels and 60 frames per second currently available in the 2D video world. Hence, our efforts are focused on parallel algorithms for the 3D reconstruction processes to achieve 2D performance limits but with 3D content.

# 3.2 Patterns

To make parallel programming easier, we must improve the way we think about parallel programming. Since "clear language breeds clear thinking," we need better ways of describing and teaching parallel programming

activities. Thus, in addition to teaching language features and algorithms, we should also teach patterns used in parallel programming. Expert programmers think about programs at a higher level than beginners. They see relationships between different parts of a program and understand the problems that these relationships solve. Courses and books on parallel programming have tended to focus either on parallel algorithms or on programming languages or lower-level programming models that are used to write parallel programs, but do not teach about software structure and higher-level patterns. Documenting and teaching these patterns should enable more programmers to become experts faster. The patterns can also become a vocabulary for documenting programs and for letting programmers talk about the programs they are designing. Programming languages evolve to better support the most common patterns, and sometimes libraries are designed to automate some patterns. So better understanding the patterns of parallel programming can make parallel programming easier.

The most widely used book on (sequential) software patterns is *Design Patterns* [11], co-authored by one of us, which focuses on object-oriented design. These are relatively low-level patterns that are easy to map down to code. There are a lot of higher-level patterns common to object-oriented programming that are not described in the book, but the patterns in the book have been useful on their own and have been good enough to teach people the style of object-oriented programming.

Work on parallel programming patterns has been going on for some years (papers on parallel patterns are regularly presented at Pattern Language of Programs (PLoP) conferences). Unfortunately, the work has not been as successful as the work of patterns for sequential programming. Some noteworthy efforts are the book by Doug Lea [53] covering low-level parallel programming patterns in the context of the Java threading model, the book by Mattson et. al [54] focusing on high-level patterns that are technology-independent, and Phil Colella's original identification of seven *dwarfs* or categories of applications that cover much of scientific computing [55] (these were later extended to thirteen *motifs* by the UPCRC—Berkeley team [55]). However, much work still needs to be done. In general, the conversion of sequential code to a parallel one may require the development of new parallel algorithms—the programmer may need to discover opportunities for parallelism, make high-level decisions on strategies for the distribution of computation and data, and then decide how to implement the parallelism and synchronization. To be effective, the patterns effort must aid in the navigation of both the high- and low-level patterns that this process encompasses.

As a concrete example, consider one of the high-level seven *dwarfs*, namely *particle codes*. All solutions to this problem share the fact that there is a set of particles in a current state, and the next state is determined by computing and integrating the force on each particle. The solutions differ in how to compute the interaction forces between pairs of particles. The naïve approach is all-pairs but is often the best choice when the number of particles is small. In case of a uniform distribution of particles, one can use a grid to store the nearest neighboring particles for each region of space. If collision is not important, the Particle-Mesh method uses an FFT to solve the problem. For systems with a more clustered distribution of particles, such as astronomical systems, it is faster to group particles and to compute the force produced by a group. Particles can be organized into a hierarchy so that the particles affecting a given particle can be found in logarithmic time, and the Fast Multipole Method can compute an approximated force on a given particle in constant time if the right hierarchy is used. Depending on the particle distribution and application, this hierarchy can be a position tree, a region tree, a kD-tree, or a binary-space-partition tree. These are not only different algorithms; they have completely different patterns of parallelism. The naïve approach uses *task parallelism*, while the others use

*divide and conquer*, and there are other algorithms that use *geometric decomposition*. Finally, the implementation of these algorithms will differ, according to the target architecture and the selected programming language and run-time (different shared memory models vs. distributed memory vs. SIMD, fixed number of processes vs. run-time load balancing, etc.). Analogous choices arise in the spatial data structures functionality for our dynamic virtual environments applications, as described in Section 3.1.1). A good pattern language must guide a programmer through all these choices.

Although there will be a lot of patterns for parallel programming, most projects will use only a small subset since they will use a particular programming model and require only a few categories of algorithms. A key research challenge is determining how to organize the pattern catalog in a way that is meaningful to programmers and that naturally leads them to the patterns they need.

We believe that the work of documenting patterns is too big for any small group to finish. Success requires a community effort that involves not only academia but also practitioners in industry and national labs and students: pattern languages evolve through a continued interaction between writers documenting patterns, experts reviewing their documentation, programmers using the patterns and students learning patterns. Writers must learn how readers misinterpret and misuse the patterns, and rewrite them to prevent these problems. It is our goal to foster such interaction and create a broad community involved in the development of parallel pattern languages through workshops, courses, and online fora.

We are working to create a body of parallel programming patterns in several ways. First, we are documenting patterns. We are focusing on patterns that are important to us and that are not well documented already. This will include low-level patterns of the technologies we use (e.g. deterministic shared memory and actors) and high-level motifs used by our applications. Second, we are working with other authors to help improve their patterns. Third, we plan to use patterns to teach parallel programming. Experience using our patterns and the patterns of other people will help us to improve the patterns. Fourth, we plan to organize workshops for authors of parallel programming patterns, similar in style to the Pattern Languages of Programming conferences held for years at Illinois. This will bring authors together, reduce duplicated effort, and help concentrate work on the most needed patterns. Fifth, we will organize events for practitioners to both teach them patterns and to get feedback on how they use the patterns. It is easier to try this out on students, but the reaction from practitioners will not be the same, so it is important for pattern authors to hear directly from practitioners.

Documenting parallel programming patterns can have a big impact on parallel programming. Language designers will use them to test the expressiveness of their language. Tool developers will try to automate particular patterns. However, our main interest is in using them to teach the next generation of parallel programmers, whether they are in school or are already professional programmers. Thus, our main goal for the next few years is on discovering the patterns that are most important in parallel programming and in ensuring that they are documented in a way that is easy to understand and to use correctly.

# 4.1 Disciplined Shared Memory

Shared memory parallel programming languages have been around for decades. Recent examples include C++ with threads or with the OpenMP parallel constructs [56], Java [57] and C# [58]– these languages support object oriented programming, which is essential for their broad use. The use of a shared memory programming model facilitates the expression of many algorithms, but in its current incarnations, it does not offer adequate protection from program defects. Our goal is to develop disciplined shared memory models and languages that, to the extent possible, minimize concurrency related defects by design, without giving up the conveniences of modern object-oriented languages and the expressivity and performance of low-level programming.

**Data-race-free**—a **fundamental discipline:** There is broad consensus that *data races* are a fundamental source of concurrency related bugs in shared memory programs. Data races involve unsynchronized, conflicting accesses to memory, which result in unpredictable, schedule-dependent, and platform-dependent results. There is extensive literature on the difficulties introduced by data races, their classification and formalization, static and dynamic strategies for their detection, and their relation to memory models, including much of our own early work [59, 60, 61, 62, 63, 64, 65, 66]. Many have argued that programs should avoid data races so that the outcome is determined by the order in which synchronization operations execute. In fact, recent efforts on memory models for shared-memory languages have shown that it is extraordinarily difficult even to formalize acceptable semantics for programs with data races. Thus, Java [13] and the upcoming C++ memory model [14] both discourage the use of data races. Unfortunately, neither language prevents the programmer from introducing a data race. C++ leaves the semantics of a program with a data race undefined, an unacceptable strategy for safe languages such as Java. Java provides semantics with data races, but they are too complex for most programmers or system designers.

We believe that a fundamental requirement for safe shared memory programming is that races be avoided or detected [29], resulting in well-defined exceptions. Race avoidance or detection are the only practical ways of enforcing the safety of shared memory parallel code and of providing a feasible shared memory model. Debugging and testing of race-free programs is simpler since there are fewer interleaving sequences to consider—only the (possibly non-deterministic) interleaving of synchronization operations.

**Determinism**—a stronger discipline: A stronger requirement is that programs be *deterministic* so that, for each input, there is a unique output. While such a program may execute in parallel, the outcome is equivalent to that obtained in a sequential execution, and the relative timing of the executing threads cannot possibly affect the outcome. Programs satisfying this requirement have *sequential semantics*, which yields several major benefits. Such a program can be understood without concern for execution interleavings, data races, or complex memory models. Programmers can *reason* about programs, *debug* them during development, and *diagnose* error reports after deployment using familiar development patterns and tools used for sequential programs. ISVs can *test* codes more easily, without being concerned about the need to cover multiple possible executions for each input. Programmers can use an incremental parallelization and tuning strategy, progressively replacing sequential constructs with parallel constructs, while preserving program behavior. Finally,

two separately developed but deterministic parallel components should be far easier to compose than more general parallel code because, with a deterministic language, a deterministic component should have the same behavior regardless of the external context within which it is executed (with some constraints on the behavior of that external context [18]).

We believe that many transformative programs (where parallelism is used only for performance and is not part of the problem specification) can be expressed in deterministic terms. Nevertheless, non-deterministic behavior may be needed for the efficient implementation of some parallel algorithms. For example, parallel associative reductions are often scheduled in an order that depends on the number of executing threads, resulting in schedule-dependent rounding differences that users may be willing to tolerate. A parallel connected components algorithm will always return the same connected components, but may return different spanning trees for each component. Branch-and-bound search and clustering algorithms are other relevant examples.

Our fundamental thesis is that *client-side parallel programming must be deterministic by default*. Non-deterministic behavior should occur only when explicitly non-deterministic constructs are used. All shared memory parallel code, whether deterministic or non-deterministic, must be *data-race-free*: unsynchronized conflicting accesses to shared memory must result in compile-time errors or run-time exceptions.

Where possible, non-deterministic behavior should be encapsulated behind interfaces with well-defined contracts such that the rest of the program can be guaranteed deterministic as long as those contracts are satisfied. Such operations are often written by expert programmers as libraries or frameworks, and widely reused. Such code may be written *to the meta* to achieve the highest performance and can be difficult to *guarantee* deterministic, but is generally well designed and thoroughly tested. Encapsulating such code helps to localize the places where debugging and testing has to cope with non-deterministic behavior. Thereafter, *trusting* such code is a practical compromise so that application programmers can obtain most of the benefits of determinism as well as the performance of highly tuned library code. Alternately, where possible, we can also use static analyses and formal methods to verify such contracts, as described in Section 5.4.

**Providing a parallel performance model:** While we have argued for a sequential semantic model (by default) for easier reasoning, we believe that for robust performance, it is important for programmers to be exposed to a *parallel performance model*. For example, consider a language where the only explicitly parallel construct is a parallel loop, and where loop iterates are required to be independent. Although the loop has serial semantics, the user can analyze performance assuming that such a loop does execute in parallel. If the iterates are not independent, then an error will occur at compile time or an exception or warning will be raised at run-time (perhaps reverting to a sequential execution). In any case, the programmer is warned if the parallelism is not achieved. We can think of the explicitly parallel loop construct as an *annotated* loop where, in addition to specifying loop semantics, the programmer provides an indication of the expected execution model and the language implementation tries to deliver that model. Languages such as OpenMP already provide such annotations, as pragmas or directives. However, incorrect directives in OpenMP may cause data races; furthermore, the expressiveness of annotations that are, syntactically, comments, is limited. We believe that we need new programming constructs in the form of *executable annotations*.

**Research questions and our approach:** To achieve the goals described in this section, we propose to add new programming constructs to existing popular object-oriented languages, such as Java, C# and, possibly, C++. We believe that using such extended languages will provide an easier path to parallelism than using

current languages or totally new languages. If parallelism is pursued using current languages, then it is achieved either by using explicit threading, or by adding directives and writing code in idioms that can be parallelized by the compiler. The former approach is bug-prone; the latter is platform-dependent. A totally new language presents an obvious porting barrier. Our preferred alternative is to add to a popular language *performance annotations*—i.e. syntax extensions that affect the performance model but not the program semantics. With this approach, refactoring tools can support the porting of existing codes as a progressive annotation process and development tools can display a semantically equivalent program in the original language (Java, C# or C++), for debugging. The annotations are not specific to a platform; further, the investment in using them has a long-term payoff because they improve programmability, clarify design decisions, and reduce maintenance costs.

Designing such an extended language that meets the diverse goals described in this section raises many important research questions:

- Disciplined Control and Synchronization: An important means to achieve the discipline we recommend is the use of well-structured parallel control flow—the equivalent of "goto-less" programming for the parallel world. As Dijkstra argued [3], structured programming results in a simple mapping from the static program to the dynamic execution state so that a program execution is easier to comprehend and debug; at the same time, the banning of goto's causes little loss of performance. Well-behaved parallel constructs such as nested parallel loops or static dataflow programs [67, 68]) (vs. arbitrary fork-join constructs) lead to a simple view of execution state, simplifying reasoning for programmers and compilers. For non-deterministic programs, high level constructs, such as atomic sections, will be preferable to explicit locks. It will be important to provide high-level parallel constructs (such as deterministic and non-deterministic parallel iterators) in order to express prevalent parallel tasking patterns in a structured way. Research is needed to evaluate the expressiveness of such constructs and ensure that no significant performance is lost by imposing such a programming discipline.

- Race detection and prevention mechanism: We expect that race avoidance or detection can be implemented efficiently through a judicious combination of language features, as described below; of compiler techniques, as described in Section 5.1; and of hardware support for race detection, as described in Section 5.3.1 Whenever possible, it is preferable to avoid data races by design, i.e., having them detected at compile time. Data races can be avoided by providing in the source code sufficient information about memory access patterns so that the compiler can analyze memory accesses and determine that no *conflicting* memory accesses may occur. Our Deterministic Parallel Java (DPJ) language [17] achieves this goal by adding region types and effect annotations to Java. The region types partition the shared variables into disjoint sets, according to their type; the effect annotations specify which sets can be accessed or updated by a particular statement. The program is legal only if two concurrent threads never have conflicting effects on the same set. The annotations enable the programmer to express the memory sharing patterns in the code, and the reasons why the code is believed to be data-race-free. The compiler verifies the annotations (no conflicting concurrent accesses). Flaws in the programmer reasoning are exposed as compile-time errors, thus facilitating debugging; and the compiler and run-time can optimize the code using the information on data sharing.

Research is needed to determine how expressive such a type and effect system can be, and how it is best supported. At a minimum, we expect that some applications will require dynamic (executable) annotation

mechanisms, relegating some checks to run-time, but still allowing for more efficient checks and more informative run-time exceptions. We would like a language design that encourages and supports *early binding* of type and effect information, but does not prevent *late binding*; and that infers as much as possible information on access patterns, thus reducing the need for explicit annotations.

- **Definition of conflicting effects:** The DPJ effect system currently supports two effects: *read* and *write*, with writes conflicting with any other effect. This effect system can be extended to support more types of operations on shared variables, with a suitable table of conflict rules. For example, associative reductions or commutative operations on concurrent data structures can be expressed via a *commutative* effect on a method; this would conflict with any other effect and would indicate that the method can be invoked in any order within a parallel phase and the final result will be unique (up to rounding errors, for floating-point reductions). As another example, the Multi-phased Shared Arrays (MSA) language [69, 70] supports three mutually exclusive effects of read, write and accumulate, and allows the access mode of an array to be changed during execution.

- *Encapsulation:* Encapsulation of non-deterministic code, as described above, could be handled using suitably defined and validated interface contracts. For example, users of a generic reduction or parallel prefix library operation should be able to define pure, associative operators, as in languages like Fortress [71]: the *pure and associative* requirement is a contract that can often be checked by the compiler, possibly relying on effect annotations. A more complex case occurs when the result is deterministic in some essential sense, but may vary in representation or other characteristics. For example, a parallel connected components algorithm will always return the same connected components, but may be non-deterministic in terms of the representations of these components. A floating point parallel prefix computation may suffer from different rounding errors, according to the order operations are applied. A final example is the mesh refinement discussed in [72] where the outcome is guaranteed to satisfy the Delaunay property although its exact form may differ across executions. Proper interfaces to such libraries raise non-trivial theoretical and pragmatic problems.

- Virtualization and Locality: Traditional thread-based shared memory programming models such as *pthreads* or Java threads use relatively heavy-weight threads and therefore generally work efficiently when the number of threads match the number of physical cores. This results in programs that are either unable to adapt to changes in the underlying processor resources or requires complex code to perform non-trivial load balancing techniques. Higher-level programming models, such as OpenMP [56], TBB [73], and Charm++ [6] virtualize CPU resources: the degree of program parallelism (concurrent tasks) need not match the number of physical cores. Such virtualization greatly improves load-balancing but may also hurt locality, and therefore performance, if the underlying run-time system, which schedules program tasks onto the physical cores, does not have the knowledge of communication patterns. The Partitioned Global Address Space (PGAS) languages such as Titanium [74], UPC [75] or CAF [76], provide some mechanisms for handling locality, but match a model of a distributed memory system with a fixed number of nodes. Neither approach is satisfactory. We plan to explore mechanisms to provide better control of locality while virtualizing physical resources, building on our experience with object-based decomposition in Charm++ [77].

# 4.2 Parallel Operators

A particularly useful form of disciplined control is provided by data parallel operators: in data-based parallelism, tasks perform the same operation on different components of a pre-existing data ensemble or a simple iteration domain. In the simple case, such as a vector sum, the operations on distinct elements are independent and perform the same amount of work. In more complex cases, the operations may take different amounts of time and may not be all independent: one needs to find and repeatedly schedule an independent subset of operations [59, 64, 69].

Data parallelism can be encapsulated inside operands defined on aggregates, such as arrays or sets and, hence, can be incorporated into traditional languages in a transparent manner. Second, because parallelism is encapsulated in the data parallel operators, it is possible to modify the implementation of these operators. Portability is achieved by providing optimized versions of the data parallel operators for different platforms including shared and distributed memory multiprocessors, SIMD processors, and combinations of these. The result is that the same code can be executed on different platforms with minimal loss of performance. Finally, data parallel operators are an effective mechanism to encapsulate non-determinism. The possible results of these non-deterministic operations could be identical or just be guaranteed to satisfy some property while differing in significant ways as discussed above.

We have extended the traditional array operators of array languages such as APL, Fortran 90, or Matlab by adding tile abstraction and well-defined parallel semantics. We thus obtained a new data type that we call Hierarchically Tiled Arrays (HTAs) which enables the direct manipulation of tiles sequentially or in parallel [19, 20]. This extension facilitates the development of array-based parallel codes that have a high degree of locality and gives programmers the ability to directly control data layout, scheduling strategy, affinity, data distribution, and communication. We are currently developing abstractions that extend data parallel operations to other classes of aggregates such as sets, graphs, or trees to enable the development of highly readable parallel non-numeric programs.

## 4.3 Metaprogramming and Autotuning

When the target machine is a multicore, productivity suffers not only due to the increased likelihood of defects, but also because of the need to make these programs efficient and scalable. Targeting multicores complicates optimization since programmers must deal with issues that do not arise in the sequential world such as load balancing and communication [78]. The natural way to address this problem is automation. Optimization tools have always been important, but their importance is now even greater since they are our only hope to compensate for the increased difficulty brought on by parallelism. In the spirit of separation of concerns and following tradition, we are developing tools whose only objective is performance optimization. The most important such tool is of course the *program optimization passes of the compiler*, but our experience indicates that compilers at least with today's technology are not sufficient to address the productivity problem and even with the support of the best compilers the development of efficient and scalable programs remains laborious. The *library generators* implemented using autotuning techniques constitute a promising new class of tools. These produce codes that achieve impressive efficiency across a wide range of machines. Some of these generators, including ATLAS, FFTW, and SPIRAL [79, 80, 22]; have gone beyond the experimental

stage and are now routinely used by library developers or as a component of commercial systems [81]. Most library generators use empirical search to find a near-optimal version. The main idea is to generate several versions of the routine being automatically implemented by replacing algorithms and changing the way they are implemented. Variations in the implementation of an algorithm include loop unrolling, vectorization, reordering statements to improve scheduling, and tiling the computation to enhance locality. The generator executes these versions on the target machine in order to evaluate them and select the one with the best performance. Although in some cases it is feasible to conduct an exhaustive search, often the space of possibilities is too large and a subset must be selected for generation and evaluation. Typically, performance is execution time, but power consumption could also be taken into account. Library generators can be conceived as *metaprograms* which embody in a single code all the versions that are to be empirically evaluated. Although the vast majority of widely known autotuning metaprograms are library routine generators, metaprograms implementing complete applications are also of great importance when the bulk of the computation cannot be implemented in terms of existing libraries.

The autotuning approach has the advantage over compilers that it can make use of semantic information that typically would not be available to compilers, but this information must in some cases be provided by the programmer and this means extra work. However, the effectiveness with which these autotuning systems enable portability across machines and machine generations has made the extra effort worthwhile in the past because although the initial effort is higher than that required to develop a highly tuned version for a single machine, porting to new machines becomes much simpler. We expect the impact of these systems on productivity to be even greater when dealing with parallelism. Furthermore, we believe that many applications can benefit from autotuning without the intervention of programmers if the application is written in terms of routines for which there exist a generator or in terms of other primitives such as codelets or data parallel operations (see below).

There are several important issues that must be addressed. In fact, today's developers of autotuning software must do all the work from scratch with practically no software support and therefore we must study techniques to increase the applicability of autotuning. Therefore, building on our earlier work on library generators, we are working to make metaprogramming for autotuning a more useful and effective methodology so that it can become one of the foundations of productivity for multicores. In particular, we are studying and developing abstractions and tools to facilitate the implementation of parallel self-tuning codes, such as the ones outlined next:

- Continue advancing our understanding of data-dependent autotuning. In many cases, the best version of a computation depends on the input data. For example, many sorting algorithms perform differently for different input data sets and the choice of the best algorithm is therefore data dependent. We need runtime selection to enable data-dependent optimization. One possibility is to generate code that contains multiple semantically equivalent versions of the computation, one of which is selected at execution time. Alternatively, autotuning could be done at execution time. The impact of runtime selection on performance is demonstrated by our studies on the autotuning of sorting [23, 24].

- Develop languages for metaprogramming and autotuning. This metalanguage should describe collections of valid implementations, ways to combine code components, and possible values of implementation parameters. This metalanguage should also make it possible to specify strategies for the identification of optimal points in the space of implementations for each target machine. The metaprograms could implement

libraries or complete applications. One of our goals is to study the complexity of these metaprograms. We believe that, with the appropriate design, metaprogramming will dramatically facilitate the initial tuning and subsequent porting to new generations of machines. This work will build on our experience with a prototype metalanguage called X-language [82].

- Implement autotuning versions of the parallel operators discussed in the previous section. Autotuning versions of these operators will facilitate portability across classes of parallel machines, including muticores, multicomputers, and SIMD processors, and will enable powerful optimizations.

- Design and development of a codelet-based optimization strategy. Codelets are computational blocks that occur sufficiently often in programs that it is worth developing manual and/or automatic techniques to (i) isolate them within the context of large programs, and (ii) optimize their performance, possibly using customized approaches. We plan to search for codelets by analyzing source programs statically and binaries dynamically. Our strategy is to optimize programs by recognizing and replacing codelets with improved versions. As mentioned above, with autotuning versions of codelets and data parallel operators, it will be possible to bring the benefit of autotuning to numerous programs without the need for programmer intervention.