# RISC-V Cryptography Extensions Volume I Scalar & Entropy Source Instructions

Version v1.0.1, 18<sup>th</sup> Feb, 2022: Ratified

# Table of Contents

| C  | olophon                                                   | . 1 |

|----|-----------------------------------------------------------|-----|

| Α  | cknowledgments                                            | . 2 |

| Cl | nangelog                                                  | . 3 |

| 1. | Introduction                                              | . 4 |

|    | 1.1. Intended Audience                                    | . 4 |

|    | 1.2. Sail Specifications                                  | . 5 |

|    | 1.3. Policies                                             | . 5 |

| 2. | Extensions Overview                                       | . 6 |

|    | 2.1. Zbkb - Bitmanip instructions for Cryptography        | . 6 |

|    | 2.2. Zbkc - Carry-less multiply instructions              | . 7 |

|    | 2.3. Zbkx - Crossbar permutation instructions             | . 7 |

|    | 2.4. Zknd - NIST Suite: AES Decryption                    | . 8 |

|    | 2.5. Zkne - NIST Suite: AES Encryption                    | . 8 |

|    | 2.6. Zknh - NIST Suite: Hash Function Instructions        | . 8 |

|    | 2.7. Zksed - ShangMi Suite: SM4 Block Cipher Instructions | . 9 |

|    | 2.8. Zksh - ShangMi Suite: SM3 Hash Function Instructions | . 9 |

|    | 2.9. Zkr - Entropy Source Extension                       | . 9 |

|    | 2.10. Zkn - NIST Algorithm Suite                          | . 9 |

|    | 2.11. Zks - ShangMi Algorithm Suite                       | 10  |

|    | 2.12. Zk - Standard scalar cryptography extension         | 10  |

|    | 2.13. Zkt - Data Independent Execution Latency            | 10  |

| 3. | Instructions                                              | 11  |

|    | 3.1. aes32dsi                                             | 11  |

|    | 3.2. aes32dsmi                                            | 12  |

|    | 3.3. aes32esi                                             | 13  |

|    | 3.4. aes32esmi                                            | 14  |

|    | 3.5. aes64ds                                              | 15  |

|    | 3.6. aes64dsm                                             | 16  |

|    | 3.7. aes64es                                              | 17  |

|    | 3.8. aes64esm                                             | 18  |

|    | 3.9. aes64im                                              | 19  |

|    | 3.10. aes64ks1i                                           | 20  |

|    | 3.11. aes64ks2                                            | 21  |

|    | 3.12. andn                                                | 22  |

|    | 3.13. brev8                                               | 23  |

|    | 3.14. clmul                                               | 24  |

|    | 3.15. clmulh                                              | 25  |

|    | 3.16. orn                                                 | 26  |

|    | 3.17. pack                                                | 27  |

|    | 3.18. packh                                               | 28  |

|    | 3.19. packw                                               | 29  |

|    | 3.20 rev8                                                 | 30  |

|    | 3.21. rol                                              | . 31 |

|----|--------------------------------------------------------|------|

|    | 3.22. rolw                                             | . 32 |

|    | 3.23. ror                                              | . 33 |

|    | 3.24. rori                                             | . 34 |

|    | 3.25. roriw                                            | . 35 |

|    | 3.26. rorw                                             | . 36 |

|    | 3.27. sha256sig0                                       | . 37 |

|    | 3.28. sha256sig1                                       | . 38 |

|    | 3.29. sha256sum0                                       | . 39 |

|    | 3.30. sha256sum1                                       | . 40 |

|    | 3.31. sha512sig0h                                      | . 41 |

|    | 3.32. sha512sig0l                                      | . 42 |

|    | 3.33. sha512sig1h                                      | . 43 |

|    | 3.34. sha512sig1l                                      | . 44 |

|    | 3.35. sha512sum0r                                      | . 45 |

|    | 3.36. sha512sum1r                                      | . 46 |

|    | 3.37. sha512sig0                                       | . 47 |

|    | 3.38. sha512sig1                                       | . 48 |

|    | 3.39. sha512sum0                                       | . 49 |

|    | 3.40. sha512sum1                                       | . 50 |

|    | 3.41. sm3p0                                            | . 51 |

|    | 3.42. sm3p1                                            | . 52 |

|    | 3.43. sm4ed                                            | . 53 |

|    | 3.44. sm4ks                                            | . 54 |

|    | 3.45. unzip                                            | . 55 |

|    | 3.46. xnor                                             | . 56 |

|    | 3.47. xperm8                                           | . 57 |

|    | 3.48. xperm4                                           |      |

|    | 3.49. zip                                              | . 59 |

| 4. | Entropy Source                                         | . 60 |

|    | 4.1. The seed CSR                                      | . 60 |

|    | 4.2. Entropy Source Requirements                       | . 61 |

|    | 4.2.1. NIST SP 800-90B / FIPS 140-3 Requirements       | . 62 |

|    | 4.2.2. BSI AIS-31 PTG.2 / Common Criteria Requirements | . 62 |

|    | 4.2.3. Virtual Sources: Security Requirement           |      |

|    | 4.3. Access Control to seed                            | . 63 |

| 5. | Data Independent Execution Latency Subset: Zkt         | . 65 |

|    | 5.1. Scope and Goal                                    |      |

|    | 5.2. Background                                        | . 66 |

|    | 5.3. Specific Instruction Rationale.                   | . 66 |

|    | 5.4. Programming Information                           |      |

|    | 5.5. Zkt listings                                      |      |

|    | 5.5.1. RVI (Base Instruction Set)                      | . 67 |

|    | 5.5.2. RVM (Multiply)                                  |      |

|    | 5.5.3. RVC (Compressed)                                |      |

|    |                                                        |      |

| 5.5.4. RVK (Scalar Cryptography)                                        | . 69 |

|-------------------------------------------------------------------------|------|

| 5.5.5. RVB (Bitmanip)                                                   | . 70 |

| 6. Bibliography                                                         | . 72 |

| Appendix A: Instruction Rationale                                       | . 77 |

| A.1. AES Instructions                                                   | . 77 |

| A.2. SHA2 Instructions                                                  | . 77 |

| A.3. SM3 and SM4 Instructions                                           | . 77 |

| A.4. Bitmanip Instructions for Cryptography                             | . 77 |

| A.4.1. Rotations                                                        | . 77 |

| A.4.2. Bit & Byte Permutations                                          | . 78 |

| A.4.3. Carry-less Multiply                                              | . 79 |

| A.4.4. Logic With Negate                                                | . 79 |

| A.4.5. Packing                                                          | . 79 |

| A.4.6. Crossbar Permutation Instructions                                | . 80 |

| Appendix B: Entropy Source Rationale and Recommendations                | . 81 |

| B.1. Checklists for Design and Self-Certification                       | . 81 |

| B.2. Standards and Terminology                                          | . 82 |

| B.2.1. Entropy Source (ES)                                              | . 82 |

| B.2.2. Conditioning: Cryptographic and Non-Cryptographic                | . 83 |

| B.2.3. Pseudorandom Number Generator (PRNG)                             | . 83 |

| B.2.4. Deterministic Random Bit Generator (DRBG)                        | . 83 |

| B.3. Specific Rationale and Considerations                              | . 83 |

| B.3.1. (Section 4.1) The seed CSR                                       | . 83 |

| B.3.2. (Section 4.2.1) NIST SP 800-90B                                  | . 84 |

| B.3.3. (Section 4.2.2) BSI AIS-31                                       | . 84 |

| B.3.4. (Section 4.2.3) Virtual Sources                                  | . 85 |

| B.3.5. (Section 4.3) Security Considerations for Direct Hardware Access | . 85 |

| B.4. Security Controls and Health Tests                                 | . 86 |

| B.4.1. T1: On-demand testing                                            | . 86 |

| B.4.2. T2: Continuous checks                                            | . 86 |

| B.4.3. T3: Fatal error states                                           | . 87 |

| B.4.4. Information Flows                                                | . 87 |

| B.5. Implementation Strategies                                          | . 87 |

| B.5.1. Ring Oscillators                                                 | . 88 |

| B.5.2. Shot Noise                                                       | . 88 |

| B.5.3. Other types of noise                                             | . 88 |

| B.5.4. Continuous Health Tests                                          | . 89 |

| B.5.5. Non-cryptographic Conditioners                                   | . 89 |

| B.5.6. Cryptographic Conditioners                                       | . 90 |

| B.5.7. The Final Random: DRBGs                                          | . 90 |

| B.5.8. Quantum vs. Classical Random                                     | . 90 |

| B.5.9. Post-Quantum Cryptography                                        | . 91 |

| B.6. Suggested GetNoise Test Interface                                  | . 91 |

| Appendix C: Supplementary Materials.                                    | . 93 |

| Appendix D: Supporting Sail Code                                        | . 94 |

# Colophon

This document describes the Scalar Cryptography extensions to the RISC-V Instruction Set Architecture.

This document is in the Ratified state. No changes are allowed. Any desired or needed changes can be the subject of a follow-on new extension. Ratified extensions are never revised. For more information, see here.

Copyright and licensure:

This work is licensed under a Creative Commons Attribution 4.0 International License

Document Version Information:

master @ 16ddcca3a52f940bbba5a9425f171cd5e7401254

See github.com/riscv/riscv-crypto for more information.

# Acknowledgments

Contributors to all versions of the specification (in alphabetical order) include:

Alexander Zeh, Andy Glew, Barry Spinney, Ben Marshall (Editor), Daniel Page, Derek Atkins, Ken Dockser,

Markku-Juhani O. Saarinen, Nathan Menhorn, L Peter Deutsch, Richard Newell, Claire Wolf

We are all very grateful to the huge number of other people who have helped to improve this specification through their comments, reviews, feedback and questions.

# Changelog

| Version | Changes                                                                         |  |

|---------|---------------------------------------------------------------------------------|--|

| v1.0.1  | Fix typos to show that c.srli, c.srai, and c.slli are Zkt instructions in RV64. |  |

| v1.0.0  | Initial Release                                                                 |  |

# Chapter 1. Introduction

This document describes the *scalar* cryptography extension for RISC-V. All instructions described herein use the general-purpose X registers, and obey the 2-read-1-write register access constraint. These instructions are designed to be lightweight and suitable for 32 and 64 bit base architectures; from embedded IoT class cores to large, application class cores which do not implement a vector unit.

This document also describes the architectural interface to an Entropy Source, which can be used to generate cryptographic secrets. This is found in Chapter 4.

It also contains a mechanism allowing core implementers to provide "Constant Time Execution" guarantees in Chapter 5.

A companion document *Volume II: Vector Instructions*, describes instruction proposals which build on the RISC-V Vector Extension. The Vector Cryptography extension is currently a work in progress waiting for the base Vector extension to stabilise. We expect to pick up this work in earnest in Q4-2021 or Q1-2022.

### 1.1. Intended Audience

Cryptography is a specialised subject, requiring people with many different backgrounds to cooperate in its secure and efficient implementation. Where possible, we have written this specification to be understandable by all, though we recognise that the motivations and references to algorithms or other specifications and standards may be unfamiliar to those who are not domain experts.

This specification anticipates being read and acted on by various people with different backgrounds. We have tried to capture these backgrounds here, with a brief explanation of what we expect them to know, and how it relates to the specification. We hope this aids people's understanding of which aspects of the specification are particularly relevant to them, and which they may (safely!) ignore or pass to a colleague.

#### Cryptographers and cryptographic software developers

These are the people we expect to write code using the instructions in this specification. They should understand fairly obviously the motivations for the instructions we include, and be familiar with most of the algorithms and outside standards to which we refer. We expect the sections on constant time execution (Chapter 5) and the entropy source (Chapter 4) to be chiefly understood with their help.

#### Computer architects

We do not expect architects to have a cryptography background. We nonetheless expect architects to be able to examine our instructions for implementation issues, understand how the instructions will be used in context, and advise on how best to fit the functionality the cryptographers want to the ISA interface.

#### Digital design engineers & micro-architects

These are the people who will implement the specification inside a core. Again, no cryptography expertise is assumed, but we expect them to interpret the specification and anticipate any hardware implementation issues, e.g., where high-frequency design considerations apply, or where latency/area tradeoffs exist etc. In particular, they should be aware of the literature around efficiently implementing AES and SM4 SBoxes in hardware.

#### Verification engineers

Responsible for ensuring the correct implementation of the extension in hardware. No cryptography background is assumed. We expect them to identify interesting test cases from the specification. An understanding of their real-world usage will help with this. We do not expect verification engineers in this sense to be experts in entropy source design or certification, since this is a very specialised area. We do expect them however to identify all of the *architectural* test cases around the entropy source interface.

These are by no means the only people concerned with the specification, but they are the ones we considered most while writing it.

### 1.2. Sail Specifications

RISC-V maintains a formal model of the ISA specification, implemented in the Sail ISA specification language [ 1]. Note that *Sail* refers to the specification language itself, and that there is a *model* of *RISC-V*, written using Sail. It is not correct to refer to "the Sail model". This is ambiguous, given there are many models of different ISAs implemented using Sail. We refer to the Sail implementation of RISC-V as "the RISC-V Sail model".

The Cryptography extension uses inline Sail code snippets from the actual model to give canonical descriptions of instruction functionality. Each instruction is accompanied by its expression in Sail, and includes calls to supporting functions which are too verbose to include directly in the specification. This supporting code is listed in Appendix D. The Sail Manual is recommended reading in order to best understand the code snippets.

Note that this document contains only a subset of the formal model: refer to the formal model Github repository for the complete model.

### 1.3. Policies

In creating this proposal, we tried to adhere to the following policies:

- Where there is a choice between: 1) supporting diverse implementation strategies for an algorithm or 2) supporting a single implementation style which is more performant / less expensive; the crypto extension will pick the more constrained but performant option. This fits a common pattern in other parts of the RISC-V specification, where recommended (but not required) instruction sequences for performing particular tasks are given as an example, such that both hardware and software implementers can optimise for only a single use-case.

- The extension will be designed to support *existing* standardised cryptographic constructs well. It will not try to support proposed standards, or cryptographic constructs which exist only in academia. Cryptographic standards which are settled upon concurrently with or after the RISC-V cryptographic extension standardisation will be dealt with by future additions to, or versions of, the RISC-V cryptographic standard extension. It is anticipated that the NIST Lightweight Cryptography contest and the NIST Post-Quantum Cryptography contest may be dealt with this way, depending on timescales.

- Historically, there has been some discussion [39] on how newly supported operations in general-purpose computing might enable new bases for cryptographic algorithms. The standard will not try to anticipate new useful low-level operations which *may* be useful as building blocks for future cryptographic constructs.

- Regarding side-channel countermeasures: Where relevant, proposed instructions must aim to remove the

possibility of any timing side-channels. For side-channels based on power or electro-magnetic (EM)

measurements, the extension will not aim to support countermeasures which are implemented above the ISA

abstraction layer. Recommendations will be given where relevant on how micro-architectures can implement

instructions in a power/EM side-channel resistant way.

## Chapter 2. Extensions Overview

The group of extensions introduced by the Scalar Cryptography Instruction Set Extension is listed here.

Detection of individual cryptography extensions uses the unified software-based RISC-V discovery method.

At the time of writing, these discovery mechanisms are still a work in progress.

A note on extension rationale

Specialist encryption and decryption instructions are separated into different functional groups because some use cases (e.g., Galois/Counter Mode in TLS 1.3) do not require decryption functionality.

The NIST and ShangMi algorithms suites are separated because their usefulness is heavily dependent on the countries a device is expected to operate in. NIST ciphers are a part of most standardised internet protocols, while ShangMi ciphers are required for use in China.

### 2.1. Zbkb - Bitmanip instructions for Cryptography

These are a subset of the Bitmanipulation Extension Zbb which are particularly useful for Cryptography.

Some of these instructions are defined in the first Bitmanip ratification package, and some are not ( pack, packh, packw, brev8, zip, unzip). All of the instructions in Zbkb have their complete specification included in this document, including those *not* present in the initial Bitmanip ratification package. This is to make the present specification complete as a standalone document. Inevitably there might be small divergences between the Bitmanip and Scalar Cryptography specification documents as they move at different paces. When this happens, assume that the Bitmanip specification has the most up-to-date version of Bitmanip instructions. This is an unfortunate but necessary stop-gap while Scalar Cryptography and Bitmanip are being rapidly iterated on prior to public review.

| RV32     | RV64     | Mnemonic | Instruction                          |

|----------|----------|----------|--------------------------------------|

| <b>√</b> | <b>✓</b> | ror      | Rotate right (Register)              |

| <b>✓</b> | <b>✓</b> | rol      | Rotate left (Register)               |

| <b>✓</b> | <b>✓</b> | rori     | Rotate right (Immediate)             |

|          | <b>✓</b> | rorw     | Rotate right Word (Register)         |

|          | <b>✓</b> | rolw     | Rotate Left Word (Register)          |

|          | <b>✓</b> | roriw    | Rotate right Word (Immediate)        |

| <b>✓</b> | <b>✓</b> | andn     | AND with inverted operand            |

| <b>✓</b> | <b>✓</b> | orn      | OR with inverted operand             |

| <b>✓</b> | <b>✓</b> | xnor     | Exclusive NOR                        |

| <b>✓</b> | <b>✓</b> | pack     | Pack low halves of registers         |

| <b>✓</b> | <b>✓</b> | packh    | Pack low bytes of registers          |

|          | <b>✓</b> | packw    | Pack low 16-bits of registers (RV64) |

| RV32     | RV64     | Mnemonic | Instruction           |

|----------|----------|----------|-----------------------|

| <b>✓</b> | <b>✓</b> | brev8    | Reverse bits in bytes |

| <b>✓</b> | <b>✓</b> | rev8     | Byte-reverse register |

| <b>✓</b> |          | zip      | Zip                   |

| <b>✓</b> |          | unzip    | Unzip                 |

### 2.2. Zbkc - Carry-less multiply instructions

Constant time carry-less multiply for Galois/Counter Mode. These are separated from the Zbkb because they have a considerable implementation overhead which cannot be amortised across other instructions.

These instructions are defined in the first Bitmanip ratification package for the Zbc extension. All of the instructions in Zbkc have their complete specification included in this document, including those *not* present in the initial Bitmanip ratification package. This is to make the present specification complete as a standalone document. Inevitably there might be small divergences between the Bitmanip and Scalar Cryptography specification documents as they move at different paces. When this happens, assume that the Bitmanip specification has the most up-to-date version of Bitmanip instructions. This is an unfortunate but necessary stopgap while Scalar Cryptography and Bitmanip are being rapidly iterated on prior to public review.

| RV32     | RV64     | Mnemonic | Instruction                     |

|----------|----------|----------|---------------------------------|

| <b>✓</b> | <b>✓</b> | clmul    | Carry-less multiply (low-part)  |

| <b>✓</b> | <b>✓</b> | clmulh   | Carry-less multiply (high-part) |

### 2.3. Zbkx - Crossbar permutation instructions

These instructions are useful for implementing SBoxes in constant time, and potentially with DPA protections. These are separated from the Zbkb because they have an implementation overhead which cannot be amortised across other instructions.

All of these instructions are missing from the first Bitmanip ratification package. Hence, all of the instructions in Zbkx have their complete specification included in this document. This is to make the present specification complete as a standalone document. Inevitably there might be small divergences between the Bitmanip and Scalar Cryptography specification documents as they move at different paces. When this happens, assume that the Bitmanip specification has the most up-to-date version of Bitmanip instructions. This is an unfortunate but necessary stop-gap while Scalar Cryptography and Bitmanip are being rapidly iterated on prior to public review.

| RV32     | RV64     | Mnemonic | Instruction                    |

|----------|----------|----------|--------------------------------|

| <b>✓</b> | <b>✓</b> | xperm8   | Crossbar permutation (bytes)   |

| <b>✓</b> | <b>✓</b> | xperm4   | Crossbar permutation (nibbles) |

### 2.4. Zknd - NIST Suite: AES Decryption

Instructions for accelerating the decryption and key-schedule functions of the AES block cipher.

| RV32     | RV64     | Mnemonic  | Instruction                               |

|----------|----------|-----------|-------------------------------------------|

| <b>✓</b> |          | aes32dsi  | AES final round decrypt (RV32)            |

| <b>✓</b> |          | aes32dsmi | AES middle round decrypt (RV32)           |

|          | <b>✓</b> | aes64ds   | AES decrypt final round (RV64)            |

|          | <b>✓</b> | aes64dsm  | AES decrypt middle round (RV64)           |

|          | <b>✓</b> | aes64im   | AES Decrypt KeySchedule MixColumns (RV64) |

|          | <b>✓</b> | aes64ks1i | AES Key Schedule Instruction 1 (RV64)     |

|          | <b>✓</b> | aes64ks2  | AES Key Schedule Instruction 2 (RV64)     |

The AES Key Schedule Instruction 1 (RV64) and AES Key Schedule Instruction 2 (RV64) instructions are present in both the Zknd and Zkne extensions.

### 2.5. Zkne - NIST Suite: AES Encryption

Instructions for accelerating the encryption and key-schedule functions of the AES block cipher.

| RV32     | RV64     | Mnemonic  | Instruction                                 |

|----------|----------|-----------|---------------------------------------------|

| <b>✓</b> |          | aes32esi  | AES final round encrypt (RV32)              |

| <b>✓</b> |          | aes32esmi | AES middle round encrypt (RV32)             |

|          | <b>✓</b> | aes64es   | AES encrypt final round instruction (RV64)  |

|          | <b>✓</b> | aes64esm  | AES encrypt middle round instruction (RV64) |

|          | <b>✓</b> | aes64ks1i | AES Key Schedule Instruction 1 (RV64)       |

|          | <b>✓</b> | aes64ks2  | AES Key Schedule Instruction 2 (RV64)       |

The aes64ks1i and aes64ks2 instructions are present in both the Zknd and Zkne extensions.

### 2.6. Zknh - NIST Suite: Hash Function Instructions

Instructions for accelerating the SHA2 family of cryptographic hash functions, as specified in [49].

| RV32     | RV64     | Mnemonic   | Instruction                 |

|----------|----------|------------|-----------------------------|

| <b>✓</b> | <b>✓</b> | sha256sig0 | SHA2-256 Sigma0 instruction |

| <b>✓</b> | <b>✓</b> | sha256sig1 | SHA2-256 Sigma1 instruction |

| <b>✓</b> | <b>✓</b> | sha256sum0 | SHA2-256 Sum0 instruction   |

| <b>✓</b> | <b>✓</b> | sha256sum1 | SHA2-256 Sum1 instruction   |

| RV32     | RV64     | Mnemonic    | Instruction                        |

|----------|----------|-------------|------------------------------------|

| <b>✓</b> |          | sha512sig0h | SHA2-512 Sigma0 high (RV32)        |

| <b>✓</b> |          | sha512sig0l | SHA2-512 Sigma0 low (RV32)         |

| <b>✓</b> |          | sha512sig1h | SHA2-512 Sigma1 high (RV32)        |

| <b>✓</b> |          | sha512sig1l | SHA2-512 Sigma1 low (RV32)         |

| <b>✓</b> |          | sha512sum0r | SHA2-512 Sum0 (RV32)               |

| <b>✓</b> |          | sha512sum1r | SHA2-512 Sum1 (RV32)               |

|          | <b>✓</b> | sha512sig0  | SHA2-512 Sigma0 instruction (RV64) |

|          | <b>✓</b> | sha512sig1  | SHA2-512 Sigma1 instruction (RV64) |

|          | <b>✓</b> | sha512sum0  | SHA2-512 Sum0 instruction (RV64)   |

|          | <b>✓</b> | sha512sum1  | SHA2-512 Sum1 instruction (RV64)   |

### 2.7. Zksed - ShangMi Suite: SM4 Block Cipher Instructions

Instructions for accelerating the SM4 Block Cipher. Note that unlike AES, this cipher uses the same core operation for encryption and decryption, hence there is only one extension for it.

| RV32     | RV64     | Mnemonic | Instruction                     |  |  |  |  |  |

|----------|----------|----------|---------------------------------|--|--|--|--|--|

| <b>✓</b> | <b>✓</b> | sm4ed    | SM4 Encrypt/Decrypt Instruction |  |  |  |  |  |

| <b>✓</b> | <b>✓</b> | sm4ks    | SM4 Key Schedule Instruction    |  |  |  |  |  |

### 2.8. Zksh - ShangMi Suite: SM3 Hash Function Instructions

Instructions for accelerating the SM3 hash function.

| RV32     | RV64     | Mnemonic | Instruction      |  |  |  |  |  |  |  |

|----------|----------|----------|------------------|--|--|--|--|--|--|--|

| <b>✓</b> | <b>✓</b> | sm3p0    | SM3 P0 transform |  |  |  |  |  |  |  |

| <b>✓</b> | <b>✓</b> | sm3p1    | SM3 P1 transform |  |  |  |  |  |  |  |

### 2.9. Zkr - Entropy Source Extension

The entropy source extension defines the seed CSR at address 0x015. This CSR provides up to 16 physical entropy bits that can be used to seed cryptographic random bit generators.

See Chapter 4 for the normative specification and access control notes. Appendix B contains design rationale and further recommendations to implementers.

### 2.10. Zkn - NIST Algorithm Suite

This extension is shorthand for the following set of other extensions:

| Included Extension | Description                                    |

|--------------------|------------------------------------------------|

| Zbkb               | Bitmanipulation instructions for cryptography. |

| Zbkc               | Carry-less multiply instructions.              |

| Zbkx               | Cross-bar Permutation instructions.            |

| Zkne               | AES encryption instructions.                   |

| Zknd               | AES decryption instructions.                   |

| Zknh               | SHA2 hash function instructions.               |

A core which implements Zkn must implement all of the above extensions.

### 2.11. Zks - ShangMi Algorithm Suite

This extension is shorthand for the following set of other extensions:

| Included Extension | Description                                    |

|--------------------|------------------------------------------------|

| Zbkb               | Bitmanipulation instructions for cryptography. |

| Zbkc               | Carry-less multiply instructions.              |

| Zbkx               | Cross-bar Permutation instructions.            |

| Zksed              | SM4 block cipher instructions.                 |

| Zksh               | SM3 hash function instructions.                |

A core which implements Zks must implement all of the above extensions.

### 2.12. Zk - Standard scalar cryptography extension

This extension is shorthand for the following set of other extensions:

| Included Extension | Description                                   |

|--------------------|-----------------------------------------------|

| Zkn                | NIST Algorithm suite extension.               |

| Zkr                | Entropy Source extension.                     |

| Zkt                | Data independent execution latency extension. |

A core which implements Zk must implement all of the above extensions.

### 2.13. Zkt - Data Independent Execution Latency

This extension allows CPU implementers to indicate to cryptographic software developers that a subset of RISC-V instructions are guaranteeed to be implemented such that their execution latency is independent of the data values they operate on. A complete description of this extension is found in Chapter 5.

# Chapter 3. Instructions

### 3.1. aes32dsi

#### **Synopsis**

AES final round decryption instruction for RV32.

#### Mnemonic

```

aes32dsi rd, rs1, rs2, bs

```

#### **Encoding**

| 31 30 | 29 |     |   | 25 | 24 |    |   | 20 | 19 |     | 15 | 14 |   | 12 | 11 |    | 7 | 6 |   |   |   |   |   | 0 |

|-------|----|-----|---|----|----|----|---|----|----|-----|----|----|---|----|----|----|---|---|---|---|---|---|---|---|

| bs    | 1  | 0 1 | 0 | 1  |    | rs | 2 |    |    | rs1 |    | 0  | 0 | 0  |    | rd |   | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

#### Description

This instruction sources a single byte from rs2 according to bs. To this it applies the inverse AES SBox operation, and XOR's the result with rs1. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknd (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

### 3.2. aes32dsmi

#### **Synopsis**

AES middle round decryption instruction for RV32.

#### Mnemonic

```

aes32dsmi rd, rs1, rs2, bs

```

#### **Encoding**

| 31 30 2 | 9   |   |   | 25 | 24 |     | 20 | 19 |     | 15 | 14 |   | 12 | 11 |    | 7 | 6 |   |   |   |   |   | 0 |

|---------|-----|---|---|----|----|-----|----|----|-----|----|----|---|----|----|----|---|---|---|---|---|---|---|---|

| bs 1    | 1 0 | 1 | 1 | 1  | '  | rs2 | •  | •  | rs1 | •  | 0  | 0 | 0  | •  | rd |   | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

#### Description

This instruction sources a single byte from rs2 according to bs. To this it applies the inverse AES SBox operation, and a partial inverse MixColumn, before XOR'ing the result with rs1. This instruction must always be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknd (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

### 3.3. aes32esi

#### **Synopsis**

AES final round encryption instruction for RV32.

#### Mnemonic

```

aes32esi rd, rs1, rs2, bs

```

#### **Encoding**

| 31 30 29   | 25 24 20 | 19 15 | 14 12 11 | 7 6      | 0       |

|------------|----------|-------|----------|----------|---------|

| bs 1 0 0 0 | ) 1 rs2  | rs1   | 0 0 0    | rd 0 1 1 | 0 0 1 1 |

#### Description

This instruction sources a single byte from rs2 according to bs. To this it applies the forward AES SBox operation, before XOR'ing the result with rs1. This instruction must always be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

#### 3.4. aes32esmi

#### **Synopsis**

AES middle round encryption instruction for RV32.

#### Mnemonic

```

aes32esmi rd, rs1, rs2, bs

```

#### **Encoding**

| 31 30 29 25  | 24 20 1 | 19 15 14 | 12 11 7 | 6 0           |

|--------------|---------|----------|---------|---------------|

| bs 1 0 0 1 1 | rs2     | rs1 0 (  | ) 0 rd  | 0 1 1 0 0 1 1 |

#### Description

This instruction sources a single byte from rs2 according to bs. To this it applies the forward AES SBox operation, and a partial forward MixColumn, before XOR'ing the result with rs1. This instruction must always be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

### 3.5. aes64ds

#### **Synopsis**

AES final round decryption instruction for RV64.

#### Mnemonic

```

aes64ds rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 15 14 12 11 | 7 6    | 0         |

|---------------|----------|-------------|--------|-----------|

| 0 0 1 1 1 0 1 | rs2 rs1  | 0 0 0       | rd 0 1 | 1 0 0 1 1 |

#### Description

Uses the two 64-bit source registers to represent the entire AES state, and produces *half* of the next round output, applying the Inverse ShiftRows and SubBytes steps. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note To Software Developers

The following code snippet shows the final round of the AES block decryption. t0 and t1 hold the current round state. t2 and t3 hold the next round state.

```

aes64ds t2, t0, t1

aes64ds t3, t1, t0

```

Note the reversed register order of the second instruction.

#### Operation

```

function clause execute (AES64DS(rs2, rs1, rd)) = {

let sr : bits(64) = aes_rv64_shiftrows_inv(X(rs2)[63..0], X(rs1)[63..0]);

let wd : bits(64) = sr[63..0];

X(rd) = aes_apply_inv_sbox_to_each_byte(wd);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknd (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

### 3.6. aes64dsm

#### **Synopsis**

AES middle round decryption instruction for RV64.

#### Mnemonic

```

aes64dsm rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 15 14 12 | 11 7 6 | 0         |

|---------------|----------|----------|--------|-----------|

| 0 0 1 1 1 1 1 | rs2 rs   | 1 0 0 0  | rd 0 1 | 1 0 0 1 1 |

#### Description

Uses the two 64-bit source registers to represent the entire AES state, and produces *half* of the next round output, applying the Inverse ShiftRows, SubBytes and MixColumns steps. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note To Software Developers

The following code snippet shows one middle round of the AES block decryption. t0 and t1 hold the current round state. t2 and t3 hold the next round state.

```

aes64dsm t2, t0, t1

aes64dsm t3, t1, t0

```

Note the reversed register order of the second instruction.

#### Operation

```

function clause execute (AES64DSM(rs2, rs1, rd)) = {

let sr : bits(64) = aes_rv64_shiftrows_inv(X(rs2)[63..0], X(rs1)[63..0]);

let wd : bits(64) = sr[63..0];

let sb : bits(64) = aes_apply_inv_sbox_to_each_byte(wd);

X(rd) = aes_mixcolumn_inv(sb[63..32]) @ aes_mixcolumn_inv(sb[31..0]);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknd (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

### 3.7. aes64es

#### **Synopsis**

AES final round encryption instruction for RV64.

#### Mnemonic

```

aes64es rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25   | 24 20 19 1 | 5 14 12 11 | 7 6 0         |

|---------------|------------|------------|---------------|

| 0 0 1 1 0 0 1 | rs2 rs1    | 0 0 0 rd   | 0 1 1 0 0 1 1 |

#### Description

Uses the two 64-bit source registers to represent the entire AES state, and produces *half* of the next round output, applying the ShiftRows and SubBytes steps. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note To Software Developers

The following code snippet shows the final round of the AES block encryption. t0 and t1 hold the current round state. t2 and t3 hold the next round state.

```

aes64es t2, t0, t1

aes64es t3, t1, t0

```

Note the reversed register order of the second instruction.

#### Operation

```

function clause execute (AES64ES(rs2, rs1, rd)) = {

let sr : bits(64) = aes_rv64_shiftrows_fwd(X(rs2)[63..0], X(rs1)[63..0]);

let wd : bits(64) = sr[63..0];

X(rd) = aes_apply_fwd_sbox_to_each_byte(wd);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

### 3.8. aes64esm

#### **Synopsis**

AES middle round encryption instruction for RV64.

#### Mnemonic

```

aes64esm rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 15 14 12 1 | 11 7 6 | 0         |

|---------------|----------|------------|--------|-----------|

| 0 0 1 1 0 1 1 | rs2 rs1  | 0 0 0      | rd 0 1 | 1 0 0 1 1 |

#### Description

Uses the two 64-bit source registers to represent the entire AES state, and produces *half* of the next round output, applying the ShiftRows, SubBytes and MixColumns steps. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note To Software Developers

The following code snippet shows one middle round of the AES block encryption. t0 and t1 hold the current round state. t2 and t3 hold the next round state.

```

aes64esm t2, t0, t1

aes64esm t3, t1, t0

```

Note the reversed register order of the second instruction.

#### Operation

```

function clause execute (AES64ESM(rs2, rs1, rd)) = {

let sr : bits(64) = aes_rv64_shiftrows_fwd(X(rs2)[63..0], X(rs1)[63..0]);

let wd : bits(64) = sr[63..0];

let sb : bits(64) = aes_apply_fwd_sbox_to_each_byte(wd);

X(rd) = aes_mixcolumn_fwd(sb[63..32]) @ aes_mixcolumn_fwd(sb[31..0]);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

### 3.9. aes64im

#### **Synopsis**

This instruction accelerates the inverse MixColumns step of the AES Block Cipher, and is used to aid creation of the decryption KeySchedule.

#### Mnemonic

aes64im rd, rs1

#### **Encoding**

| 31 30 29 25   | 24 20 19 15   | 5 14 12 11 7 | 6 0           |

|---------------|---------------|--------------|---------------|

| 0 0 1 1 0 0 0 | 0 0 0 0 0 rs1 | 0 0 1 rd     | 0 0 1 0 0 1 1 |

#### Description

The instruction applies the inverse MixColumns transformation to two columns of the state array, packed into a single 64-bit register. It is used to create the inverse cipher KeySchedule, according to the equivalent inverse cipher construction in [47] (Page 23, Section 5.3.5). This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

```

function clause execute (AES64IM(rs1, rd)) = {

let w0 : bits(32) = aes_mixcolumn_inv(X(rs1)[31.. 0]);

let w1 : bits(32) = aes_mixcolumn_inv(X(rs1)[63..32]);

X(rd) = w1 @ w0;

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknd (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

#### 3.10. aes64ks1i

#### **Synopsis**

This instruction implements part of the KeySchedule operation for the AES Block cipher involving the SBox operation.

#### Mnemonic

```

aes64ks1i rd, rs1, rnum

```

#### **Encoding**

| 31 30 29 25 24  | 23 20 19 15 | 14 12 11 7 | 6 0           |

|-----------------|-------------|------------|---------------|

| 0 0 1 1 0 0 0 1 | rnum rs1    | 0 0 1 rd   | 0 0 1 0 0 1 1 |

#### Description

This instruction implements the rotation, SubBytes and Round Constant addition steps of the AES block cipher Key Schedule. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on. Note that rnum must be in the range 0x0..0xA. The values 0xB..0xF are reserved.

#### Operation

```

function clause execute (AES64KS1I(rnum, rs1, rd)) = {

if(unsigned(rnum) > 10) then {

handle_illegal(); RETIRE_SUCCESS

} else {

let tmp1 : bits(32) = X(rs1)[63..32];

let rc : bits(32) = aes_decode_rcon(rnum); /* round number -> round constant

*/

let tmp2 : bits(32) = if (rnum ==0xA) then tmp1 else ror32(tmp1, 8);

let tmp3 : bits(32) = aes_subword_fwd(tmp2);

let result : bits(64) = (tmp3 ^ rc) @ (tmp3 ^ rc);

X(rd) = EXTZ(result);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV64) | v1.0.0          | Frozen          |

| Zknd (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

### 3.11. aes64ks2

#### **Synopsis**

This instruction implements part of the KeySchedule operation for the AES Block cipher.

#### Mnemonic

```

aes64ks2 rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25 | 24 20 19 | 15 14 12 11 | 7 6 0         |

|-------------|----------|-------------|---------------|

| 0 1 1 1 1 1 | rs2 rs1  | 0 0 0 rd    | 0 1 1 0 0 1 1 |

#### Description

This instruction implements the additional XOR'ing of key words as part of the AES block cipher Key Schedule. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

```

function clause execute (AES64KS2(rs2, rs1, rd)) = {

let w0 : bits(32) = X(rs1)[63..32] ^ X(rs2)[31..0];

let w1 : bits(32) = X(rs1)[63..32] ^ X(rs2)[31..0] ^ X(rs2)[63..32];

X(rd) = w1 @ w0;

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zkne (RV64) | v1.0.0          | Frozen          |

| Zknd (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

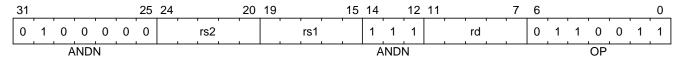

### 3.12. andn

#### **Synopsis**

AND with inverted operand

#### Mnemonic

andn rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs the bitwise logical AND operation between rs1 and the bitwise inversion of rs2.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbb ([zbb]) | v1.0.0          | Frozen          |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

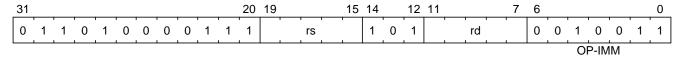

### 3.13. brev8

#### **Synopsis**

Reverse the bits in each byte of a source register.

#### Mnemonic

brev8 rd, rs

#### **Encoding**

#### Description

This instruction reverses the order of the bits in every byte of a register.

This instruction is a specific encoding of a more generic instruction which was originally proposed as part of the RISC-V Bitmanip extension (grevi). Eventually, the more generic instruction may be standardised. Until then, only the most common instances of it, such as this, are being included in specifications.

#### Operation

```

result : xlenbits = EXTZ(0b0);

foreach (i from 0 to sizeof(xlen) by 8) {

result[i+7..i] = reverse_bits_in_byte(X(rs1)[i+7..i]);

};

X(rd) = result;

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

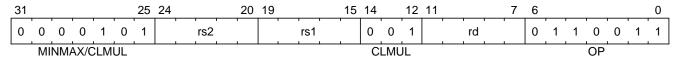

### 3.14. clmul

#### **Synopsis**

Carry-less multiply (low-part)

#### Mnemonic

clmul rd, rs1, rs2

#### **Encoding**

#### Description

clmul produces the lower half of the  $2 \cdot XLEN$  carry-less product.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbc ([zbc]) | v1.0.0          | Frozen          |

| Zbkc (Zbkc) | v1.0.0-rc4      | Frozen          |

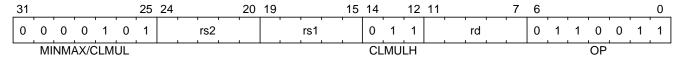

### 3.15. clmulh

#### **Synopsis**

Carry-less multiply (high-part)

#### Mnemonic

clmulh rd, rs1, rs2

#### **Encoding**

#### Description

clmulh produces the upper half of the 2-XLEN carry-less product.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbc ([zbc]) | v1.0.0          | Frozen          |

| Zbkc (Zbkc) | v1.0.0-rc4      | Frozen          |

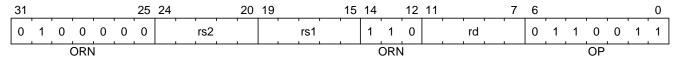

### 3.16. orn

#### **Synopsis**

OR with inverted operand

#### Mnemonic

orn rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs the bitwise logical OR operation between rs1 and the bitwise inversion of rs2.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbb ([zbb]) | v1.0.0          | Frozen          |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

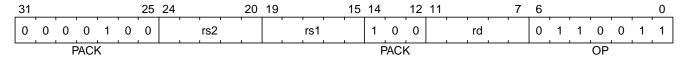

### 3.17. pack

#### **Synopsis**

Pack the low halves of rs1 and rs2 into rd.

#### Mnemonic

```

pack rd, rs1, rs2

```

#### **Encoding**

#### Description

The pack instruction packs the XLEN/2-bit lower halves of *rs1* and *rs2* into *rd*, with *rs1* in the lower half and *rs2* in the upper half.

#### Operation

```

let lo_half : bits(xlen/2) = X(rs1)[xlen/2-1..0];

let hi_half : bits(xlen/2) = X(rs2)[xlen/2-1..0];

X(rd) = EXTZ(hi_half @ lo_half);

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

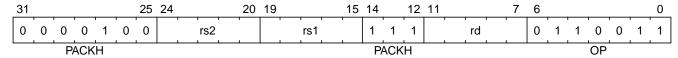

### 3.18. packh

#### **Synopsis**

Pack the low bytes of rs1 and rs2 into rd.

#### Mnemonic

```

packh rd, rs1, rs2

```

#### **Encoding**

#### Description

And the packh instruction packs the least-significant bytes of rs1 and rs2 into the 16 least-significant bits of rd, zero extending the rest of rd.

#### Operation

```

let lo_half : bits(8) = X(rs1)[7..0];

let hi_half : bits(8) = X(rs2)[7..0];

X(rd) = EXTZ(hi_half @ lo_half);

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

### 3.19. packw

#### **Synopsis**

Pack the low 16-bits of rs1 and rs2 into rd on RV64.

#### Mnemonic

```

packw rd, rs1, rs2

```

#### **Encoding**

| 31 25         | 24 20 1 | 19 15 14 1 | 12 11 7 6 | 6 2 1 0       |

|---------------|---------|------------|-----------|---------------|

| 0 0 0 0 1 0 0 | rs2     | rs1 1 0    | 0 rd (    | 0 1 1 1 0 1 1 |

#### Description

This instruction packs the low 16 bits of rs1 and rs2 into the 32 least-significant bits of rd, sign extending the 32-bit result to the rest of rd. This instruction only exists on RV64 based systems.

#### Operation

```

let lo_half : bits(16) = X(rs1)[15..0];

let hi_half : bits(16) = X(rs2)[15..0];

X(rd) = EXTS(hi_half @ lo_half);

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |

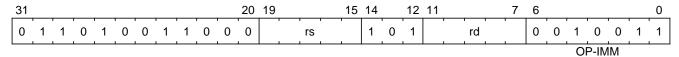

#### 3.20. rev8

#### **Synopsis**

Byte-reverse register

#### Mnemonic

rev8 rd, rs

#### **Encoding (RV32)**

#### **Encoding (RV64)**

| 31 |   |   |   |   |   |   |   |   |   |   | 20 | 19 |    | 15 | 14 |   | 12 | 11 |    |   | 7 | 6 |   |   |       |    |   | 0 |

|----|---|---|---|---|---|---|---|---|---|---|----|----|----|----|----|---|----|----|----|---|---|---|---|---|-------|----|---|---|

| 0  | 1 | 1 | 0 | 1 | 0 | 1 | 1 | 1 | 0 | 0 | 0  |    | rs |    | 1  | 0 | 1  |    | rd | , |   | 0 | 0 | 1 | 0     | 0  | 1 | 1 |

|    |   |   |   |   |   |   |   |   |   |   |    |    |    |    |    |   |    |    |    |   |   |   |   | 0 | P-IIV | lM |   |   |

#### Description

This instruction reverses the order of the bytes in rs.

This instruction is a specific encoding of a more generic instruction which was originally proposed as part of the RISC-V Bitmanip extension (grevi). Eventually, the more generic instruction may be standardised. Until then, only the most common instances of it, such as this, are being included in specifications.

#### Operation

```

let input = X(rs);

let output : xlenbits = 0;

let j = xlen - 1;

foreach (i from 0 to (xlen - 8) by 8) {

output[i..(i + 7)] = input[(j - 7)..j];

j = j - 8;

}

X[rd] = output

```

#### Software Hint

The byte-reverse operation is only available for the full register width. To emulate word-sized and halfword-sized byte-reversal, perform a rev8 rd,rs followed by a srai rd,rd.

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

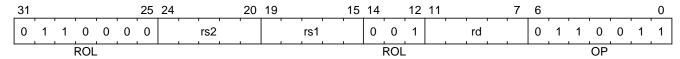

### 3.21. rol

#### **Synopsis**

Rotate Left (Register)

#### Mnemonic

rol rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs a rotate left of rs1 by the amount in least-significant log2(XLEN) bits of rs2.

#### Operation

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

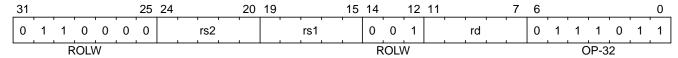

### 3.22. rolw

#### **Synopsis**

Rotate Left Word (Register)

#### Mnemonic

rolw rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs a rotate left on the least-significant word of *rs1* by the amount in least-significant 5 bits of *rs2*. The resulting word value is sign-extended by copying bit 31 to all of the more-significant bits.

#### Operation

```

let rs1 = EXTZ(X(rs1)[31..0])

let shamt = X(rs2)[4..0];

let result = (rs1 << shamt) | (rs1 >> (32 - shamt));

X(rd) = EXTS(result);

```

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

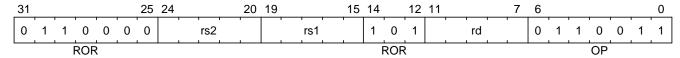

## 3.23. ror

#### **Synopsis**

Rotate Right

#### Mnemonic

ror rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs a rotate right of rs1 by the amount in least-significant log2(XLEN) bits of rs2.

#### Operation

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

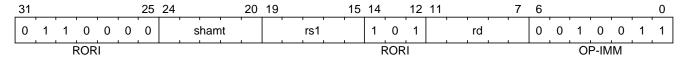

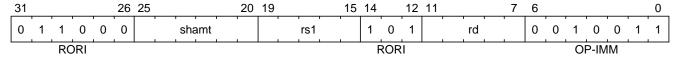

## 3.24. rori

#### **Synopsis**

Rotate Right (Immediate)

#### Mnemonic

rori rd, rs1, shamt

#### **Encoding (RV32)**

## Encoding (RV64)

#### Description

This instruction performs a rotate right of rs1 by the amount in the least-significant log2(XLEN) bits of shamt. For RV32, the encodings corresponding to shamt[5]=1 are reserved.

#### Operation

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

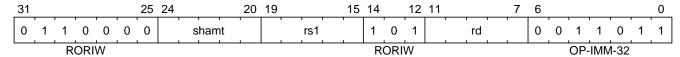

## 3.25. roriw

#### **Synopsis**

Rotate Right Word by Immediate

#### Mnemonic

roriw rd, rs1, shamt

#### **Encoding**

#### Description

This instruction performs a rotate right on the least-significant word of *rs1* by the amount in the least-significant log2(XLEN) bits of *shamt*. The resulting word value is sign-extended by copying bit 31 to all of the more-significant bits.

#### Operation

```

let rs1_data = EXTZ(X(rs1)[31..0];

let result = (rs1_data >> shamt[4..0]) | (rs1_data << (32 - shamt[4..0]));

X(rd) = EXTS(result[31..0]);</pre>

```

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

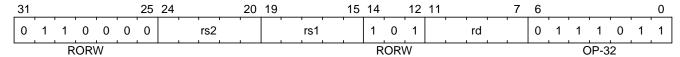

## 3.26. rorw

#### **Synopsis**

Rotate Right Word (Register)

#### Mnemonic

rorw rd, rs1, rs2

#### **Encoding**

#### Description

This instruction performs a rotate right on the least-significant word of *rs1* by the amount in least-significant 5 bits of *rs2*. The resultant word is sign-extended by copying bit 31 to all of the more-significant bits.

#### Operation

```

let rs1 = EXTZ(X(rs1)[31..0])

let shamt = X(rs2)[4..0];

let result = (rs1 >> shamt) | (rs1 << (32 - shamt));

X(rd) = EXTS(result);</pre>

```

| Extension   | Minimum version | Lifecycle state |  |  |  |

|-------------|-----------------|-----------------|--|--|--|

| Zbb ([zbb]) | v1.0.0          | Frozen          |  |  |  |

| Zbkb (Zbkb) | v1.0.0-rc4      | Frozen          |  |  |  |

# 3.27. sha256sig0

#### **Synopsis**

Implements the Sigma0 transformation function as used in the SHA2-256 hash function [49] (Section 4.1.2).

#### Mnemonic

```

sha256sig0 rd, rs1

```

#### **Encoding**

| 31 30 29 | 25 24     | 20 19    | 15 14 12 1 | 11 7 6 | 0         |

|----------|-----------|----------|------------|--------|-----------|

| 0 0 0 1  | 0 0 0 0 0 | 0 1 0 rs | 1 0 0 1    | rd 0 0 | 1 0 0 1 1 |

#### Description

This instruction is supported for both RV32 and RV64 base architectures. For RV32, the entire XLEN source register is operated on. For RV64, the low 32 bits of the source register are operated on, and the result sign extended to XLEN bits. Though named for SHA2-256, the instruction works for both the SHA2-224 and SHA2-256 parameterisations as described in [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension | Minimum version | Lifecycle state |  |  |  |  |

|-----------|-----------------|-----------------|--|--|--|--|

| Zknh      | v1.0.0          | Frozen          |  |  |  |  |

| Zkn       | v1.0.0          | Frozen          |  |  |  |  |

| Zk        | v1.0.0          | Frozen          |  |  |  |  |

## 3.28. sha256sig1

#### **Synopsis**

Implements the Sigma1 transformation function as used in the SHA2-256 hash function [49] (Section 4.1.2).

#### Mnemonic

```

sha256sig1 rd, rs1

```

#### **Encoding**

| 31 30 | 29 2    | 25 24 20    | 19 15 14 | 12 11 7 | 6 0           |

|-------|---------|-------------|----------|---------|---------------|

| 0 0   | 0 1 0 0 | 0 0 0 0 1 1 | rs1 0 0  | 1 rd    | 0 0 1 0 0 1 1 |

#### Description

This instruction is supported for both RV32 and RV64 base architectures. For RV32, the entire XLEN source register is operated on. For RV64, the low 32 bits of the source register are operated on, and the result sign extended to XLEN bits. Though named for SHA2-256, the instruction works for both the SHA2-224 and SHA2-256 parameterisations as described in [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension | Minimum version | Lifecycle state |  |  |  |  |

|-----------|-----------------|-----------------|--|--|--|--|

| Zknh      | v1.0.0          | Frozen          |  |  |  |  |

| Zkn       | v1.0.0          | Frozen          |  |  |  |  |

| Zk        | v1.0.0          | Frozen          |  |  |  |  |

## 3.29. sha256sum0

#### **Synopsis**

Implements the Sum0 transformation function as used in the SHA2-256 hash function [49] (Section 4.1.2).

#### Mnemonic

sha256sum0 rd, rs1

#### **Encoding**

| 31 30 | 29 |   |     | 25 | 24 |   |   |   | 20 | 19 |     | 15 | 14 |   | 12 | 11 |    | 7 | 6 |   |   |   |   |   | 0 |

|-------|----|---|-----|----|----|---|---|---|----|----|-----|----|----|---|----|----|----|---|---|---|---|---|---|---|---|

| 0 0   | 0  | 1 | 0 0 | 0  | 0  | 0 | 0 | 0 | 0  |    | rs1 | -  | 0  | 0 | 1  | •  | rd |   | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

#### Description

This instruction is supported for both RV32 and RV64 base architectures. For RV32, the entire XLEN source register is operated on. For RV64, the low 32 bits of the source register are operated on, and the result sign extended to XLEN bits. Though named for SHA2-256, the instruction works for both the SHA2-224 and SHA2-256 parameterisations as described in [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension | Minimum version | Lifecycle state |  |  |  |  |

|-----------|-----------------|-----------------|--|--|--|--|

| Zknh      | v1.0.0          | Frozen          |  |  |  |  |

| Zkn       | v1.0.0          | Frozen          |  |  |  |  |

| Zk        | v1.0.0          | Frozen          |  |  |  |  |

## 3.30. sha256sum1

#### **Synopsis**

Implements the Sum1 transformation function as used in the SHA2-256 hash function [49] (Section 4.1.2).

#### Mnemonic

sha256sum1 rd, rs1

#### **Encoding**

| 31 30 29 | 25 2    | 24 20     | 19 15 | 14 12 11 | 7 6     | 0     |

|----------|---------|-----------|-------|----------|---------|-------|

| 0 0 0    | 1 0 0 0 | 0 0 0 0 1 | rs1   | 0 0 1 rd | 0 0 1 0 | 0 1 1 |

#### Description

This instruction is supported for both RV32 and RV64 base architectures. For RV32, the entire XLEN source register is operated on. For RV64, the low 32 bits of the source register are operated on, and the result sign extended to XLEN bits. Though named for SHA2-256, the instruction works for both the SHA2-224 and SHA2-256 parameterisations as described in [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

| Extension | Minimum version | Lifecycle state |  |  |  |  |

|-----------|-----------------|-----------------|--|--|--|--|

| Zknh      | v1.0.0          | Frozen          |  |  |  |  |

| Zkn       | v1.0.0          | Frozen          |  |  |  |  |

| Zk        | v1.0.0          | Frozen          |  |  |  |  |

# 3.31. sha512sig0h

#### **Synopsis**

Implements the *high half* of the Sigma0 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig0h rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 15 14 12 11 | 7 6      | 0       |

|---------------|----------|-------------|----------|---------|

| 0 1 0 1 1 1 0 | rs2 rs1  | 0 0 0       | rd 0 1 1 | 0 0 1 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sigma0 transform of the SHA2-512 hash function in conjunction with the sha512sig01 instruction. The transform is a 64-bit to 64-bit function, so the input and output are each represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sigma0 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sig01 t0, a0, a1

sha512sig0h t1, a1, a0

```

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

# 3.32. sha512sig0l

#### **Synopsis**

Implements the *low half* of the Sigma0 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig0l rd, rs1, rs2

```

#### **Encoding**

| 31 30 | 29 |   |   |   | 25 | 24 |    |    | 20 | 19 |     | • | 15 ′ | 14 |   | 12 | 11 |    |     | 7 | 6 |   |   |   |   |   | 0 |

|-------|----|---|---|---|----|----|----|----|----|----|-----|---|------|----|---|----|----|----|-----|---|---|---|---|---|---|---|---|

| 0 1   | 0  | 1 | 0 | 1 | 0  |    | rs | ,2 |    |    | rs1 |   |      | 0  | 0 | 0  |    | rc | . t |   | 0 | 1 | 1 | 0 | 0 | 1 | 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sigma0 transform of the SHA2-512 hash function in conjunction with the sha512sig0h instruction. The transform is a 64-bit to 64-bit function, so the input and output are each represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sigma0 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sig0l t0, a0, a1

sha512sig0h t1, a1, a0

```

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

# 3.33. sha512sig1h

#### **Synopsis**

Implements the *high half* of the Sigma1 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig1h rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 25 | 24 20 19 | 15 14 12 11 | 7 6        | 0     |

|-------------|----------|-------------|------------|-------|

| 0 1 0 1 1 1 | rs2 rs1  | 0 0 0       | rd 0 1 1 0 | 0 1 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sigma1 transform of the SHA2-512 hash function in conjunction with the sha512sig11 instruction. The transform is a 64-bit to 64-bit function, so the input and output are each represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sigma1 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sig1l t0, a0, a1

sha512sig1h t1, a1, a0

```

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

# 3.34. sha512sig1l

#### **Synopsis**

Implements the *low half* of the Sigma1 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig1l rd, rs1, rs2

```

#### **Encoding**

| 31 30 29 2  | 5 24 20 | 19 15 | 14 12 11 | 7 6      | 0       |

|-------------|---------|-------|----------|----------|---------|

| 0 1 0 1 0 1 | rs2     | rs1   | 0 0 0    | rd 0 1 1 | 0 0 1 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sigma1 transform of the SHA2-512 hash function in conjunction with the sha512sig1h instruction. The transform is a 64-bit to 64-bit function, so the input and output are each represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sigma1 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sig1l t0, a0, a1

sha512sig1h t1, a1, a0

```

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

## 3.35. sha512sum0r

#### **Synopsis**

Implements the Sum0 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

sha512sum0r rd, rs1, rs2

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 9 13 1 <del>4</del> 17 | 2 11 7 6 | 0         |

|---------------|----------|------------------------|----------|-----------|

| 0 1 0 1 0 0 0 | rs2      | rs1 0 0 0              | rd 0 1   | 1 0 0 1 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sum0 transform of the SHA2-512 hash function. The transform is a 64-bit to 64-bit function, so the input and output is represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sum0 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sum0r t0, a0, a1

sha512sum0r t1, a1, a0

```

Note the reversed source register ordering.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

## 3.36. sha512sum1r

#### **Synopsis**

Implements the Sum1 transformation, as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

sha512sum1r rd, rs1, rs2

#### **Encoding**

| 31 30 29 25   | 24 20 19 | 15 14 12 11 7 | ' 6 0         |

|---------------|----------|---------------|---------------|

| 0 1 0 1 0 0 1 | rs2 rs1  | 0 0 0 rd      | 0 1 1 0 0 1 1 |

#### Description

This instruction is implemented on RV32 only. Used to compute the Sum1 transform of the SHA2-512 hash function. The transform is a 64-bit to 64-bit function, so the input and output is represented by two 32-bit registers. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

Note to software developers

The entire Sum1 transform for SHA2-512 may be computed on RV32 using the following instruction sequence:

```

sha512sum1r t0, a0, a1

sha512sum1r t1, a1, a0

```

Note the reversed source register ordering.

#### Operation

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV32) | v1.0.0          | Frozen          |

| Zkn (RV32)  | v1.0.0          | Frozen          |

| Zk (RV32)   | v1.0.0          | Frozen          |

# 3.37. sha512sig0

#### **Synopsis**

Implements the Sigma0 transformation function as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig0 rd, rs1

```

#### **Encoding**

| 31 30 | 29      | 25 24 20    | 19 15 | 14 12 11 | 7 6       | 0     |

|-------|---------|-------------|-------|----------|-----------|-------|

| 0 0   | 0 1 0 0 | 0 0 0 1 1 0 | rs1   | 0 0 1 r  | d 0 0 1 0 | 0 1 1 |

#### Description

This instruction is supported for the RV64 base architecture. It implements the Sigma0 transform of the SHA2-512 hash function. [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

```

function clause execute (SHA512SIGO(rs1, rd)) = {

X(rd) = ror64(X(rs1), 1) ^ ror64(X(rs1), 8) ^ (X(rs1) >> 7);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

# 3.38. sha512sig1

#### **Synopsis**

Implements the Sigma1 transformation function as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

```

sha512sig1 rd, rs1

```

#### **Encoding**

| 31 30 | 29      | 25 24     | 20 19 15 | 14 12 11 | 7 6      | 0       |

|-------|---------|-----------|----------|----------|----------|---------|

| 0 0   | 0 1 0 0 | 0 0 0 1 1 | 1 rs1    | 0 0 1    | rd 0 0 1 | 0 0 1 1 |

#### Description

This instruction is supported for the RV64 base architecture. It implements the Sigma1 transform of the SHA2-512 hash function. [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

```

function clause execute (SHA512SIG1(rs1, rd)) = {

X(rd) = ror64(X(rs1), 19) ^ ror64(X(rs1), 61) ^ (X(rs1) >> 6);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

## 3.39. sha512sum0

#### **Synopsis**

Implements the Sum0 transformation function as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

sha512sum0 rd, rs1

#### **Encoding**

| 31 3 | 30 | 29 |   |   |   | 25 | 24 |   |   |   | 20 | 19 |     | 15 | 14 |   | 12 | 11 |    | 7 | 6 |   |   |   |   |   | 0 |

|------|----|----|---|---|---|----|----|---|---|---|----|----|-----|----|----|---|----|----|----|---|---|---|---|---|---|---|---|

| 0    | 0  | 0  | 1 | 0 | 0 | 0  | 0  | 0 | 1 | 0 | 0  |    | rs1 |    | 0  | 0 | 1  |    | rd |   | 0 | 0 | 1 | 0 | 0 | 1 | 1 |

#### Description

This instruction is supported for the RV64 base architecture. It implements the Sum0 transform of the SHA2-512 hash function. [49]. This instruction must *always* be implemented such that its execution latency does not depend on the data being operated on.

#### Operation

```

function clause execute (SHA512SUMO(rs1, rd)) = {

X(rd) = ror64(X(rs1), 28) ^ ror64(X(rs1), 34) ^ ror64(X(rs1), 39);

RETIRE_SUCCESS

}

```

| Extension   | Minimum version | Lifecycle state |

|-------------|-----------------|-----------------|

| Zknh (RV64) | v1.0.0          | Frozen          |

| Zkn (RV64)  | v1.0.0          | Frozen          |

| Zk (RV64)   | v1.0.0          | Frozen          |

## 3.40. sha512sum1

#### **Synopsis**

Implements the Sum1 transformation function as used in the SHA2-512 hash function [49] (Section 4.1.3).

#### Mnemonic

sha512sum1 rd, rs1

#### **Encoding**

| 31 30 | 29 |   |   |   | 25 | 24 |   |   |   | 20 | 19 |     | 15 | 14 |   | 12 | 11 |    | 7 | 6 |   |   |   |   |   | 0 |

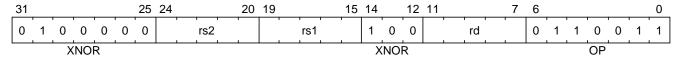

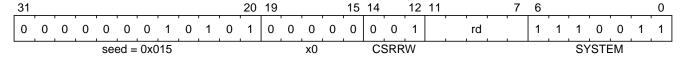

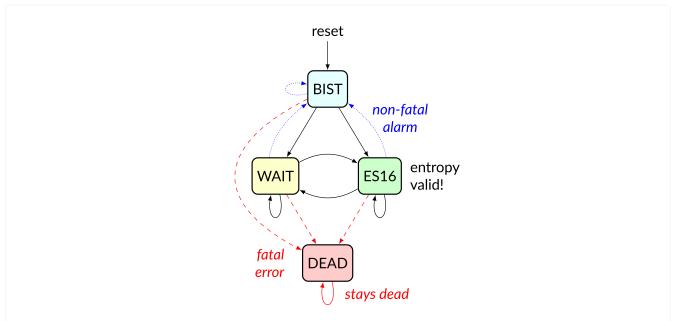

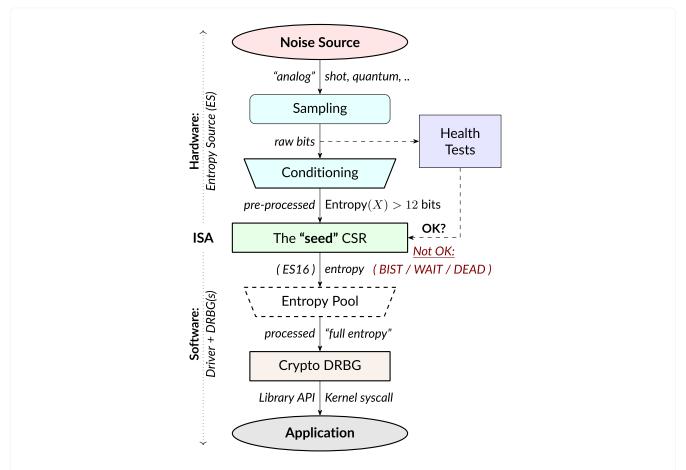

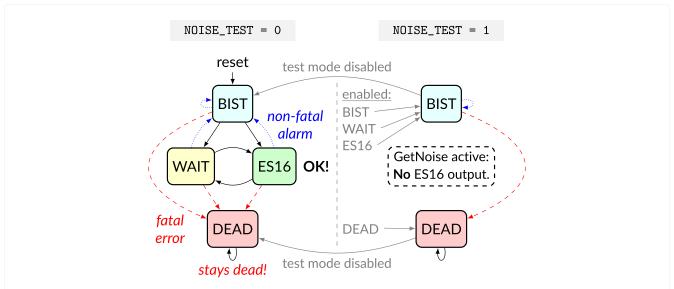

|-------|----|---|---|---|----|----|---|---|---|----|----|-----|----|----|---|----|----|----|---|---|---|---|---|---|---|---|